Eastern Mediterranean University Computer Engineering Department

# **CMPE323** MICROPROCESSORS LAB MANUAL

Dr. Mehmet Bodur

Assemblers and Development Tools for 8086 and 8051 Microprocessors

# Foreword

The objective of this book is to supply sufficient guidance to exploit the tools for developing microprocessor based design and application projects up to physical level of the implementation. The contents of is book is a collection of the hands-on experiments to practice several hardware/interfacing/software issues for an introductory level microprocessor course in a Computer Engineering program.

You may find considerable amount of practical information to guide a student in using the modern microprocessor development tools along with the classical assembly programming environments. The material is displayed in ten experimental chapters, where the first five experiments are mainly on the development and demonstration of software in 8086 assembly language, next three are on the 8051 hardware for microprocessor interface units including ports, memory, analog to digital converters and serial communication ports. Furthermore it contains two 8051 system examples with development details in higher level languages Keil-C51 C compiler. These two design examples are expected to serve for term assignments to an introductory level microprocessor course such as CMPE 323 in Computer Engineering Program of the Computer Engineering Department at Eastern Mediterranean University, where the experiments are currently carried as lab activities of CMPE 323 course.

The author of this book is aware of lots of books concentrating on both application design and practical issues on using microprocessors. In the perspective of the author, the shift of the microprocessor based applications from the assembly to the higher level languages is inevitable while the interfacing units, memory size, and processing power of the processors are developed in Moore's law, almost doubling at every two or three years.

Finally it is the authors pleasure to acknowledge his colleagues Dr. Mohammed Salamah and Prof. Dr. Hasan Komurcugil who contributed to the previously given microprocessor courses, CMPE222, CMPE 326 and CMPE328. The finalized experiments are a product of an evolution starting from the mentioned courses.

This kind of books to guide the practical applications on diverged microprocessor development tools are not expected to be error-free, although the author spent considerable effort for the correction of the errors during the practical laboratory exercise of the students who followed the included experimental procedures. The author welcomes your comments, suggestions, and corrections for the corrected editions of these laboratory notes.

Welcome to work with the microprocessors, their languages, and their development tools.

Dr. Mehmet Bodur

Assemblers and Development Tools for 8086 and 8051 Microprocessors

# Contents

| FOREWORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | III                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                                                              |

| 1. TASM, EDIT, DEBUG AND EMU8086 ASSEMBLER TOOLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                              |

| <ul> <li>1.1 OBJECTIVE</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1<br>1<br>1<br>2<br>3<br>4<br>4<br>5<br>7<br>7                 |

| <ul><li>1.3.2. Assembling with TASM</li><li>1.3.3. Assembling with Emu8086</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                |

| 2. DATA TYPES, AND EFFECT OF ALU INSTRUCTIONS ON FLAGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |

| <ul> <li>2.1 OBJECTIVE</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11<br>11<br><i>11</i>                                          |

| 3. SIMPLE VIRTUAL 8086 DEVELOPMENT BOARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

| <ul> <li>3.1 OBJECTIVE</li> <li>3.2 INTRODUCTION</li> <li>3.2.1. 8086 and main memory</li> <li>3.2.2. 8086 Processor Bus</li> <li>3.2.3. Address Latching</li> <li>3.2.4. System Configuration</li> <li>3.2.5. IO Address decoding</li> <li>3.2.6. Simple Output Port UL</li> <li>3.2.7. Simple Input Ports UA and UB</li> <li>3.2.8. Serial Communication Device</li> <li>3.3 EXPERIMENTAL PART</li> <li>3.3.1. Execution of a code on a virtual 8086 system</li> <li>3.3.2. Adding Port UA and Port UB</li> <li>3.3.3. USART and Capitalization</li> </ul> | 15<br>15<br>16<br>16<br>16<br>18<br>18<br>19<br>21<br>22<br>23 |

| 4. BIOS AND DOS SERVICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

| <ul> <li>4.1 OBJECTIVE</li> <li>4.2 PRELIMINARY STUDY</li> <li>4.3 EXPERIMENTAL PART</li> <li>4.3.1. DOS services for String Display and Input.</li> <li>4.3.2. Subroutines and Include files.</li> </ul>                                                                                                                                                                                                                                                                                                                                                    | 29<br>29<br>29                                                 |

| 5. USING SIGNED NUMBERS AND LOOK-UP TABLES                                                                                                             |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 5.1 OBJECTIVE                                                                                                                                          | 35          |

| 5.2 PRELIMINARY STUDY                                                                                                                                  |             |

| 5.3 Experimental Part                                                                                                                                  |             |

| 5.3.1. Macro Library for BIOS and DOS Services                                                                                                         |             |

| 5.3.2. Average by Signed Arithmetic Operations                                                                                                         |             |

| 5.3.3. Look-Up Table for the Square Root of an Integer                                                                                                 |             |

| 5.3.4. Simple Look-Up Table for Fibonacci Numbers                                                                                                      |             |

| 6. I/O AND EXTERNAL MEMORY INTERFACE FOR 8051                                                                                                          |             |

| 6. I/O AND EXTERNAL MEMORY INTERFACE FOR 8051                                                                                                          |             |

| 6.1 OBJECTIVE                                                                                                                                          | 45          |

| 6.2 INTRODUCTION                                                                                                                                       |             |

| 6.2.1. Typical features                                                                                                                                |             |

| 6.2.2. Registers                                                                                                                                       |             |

| 6.2.3. Instruction Set                                                                                                                                 |             |

| 6.2.4. The 8051 Ports                                                                                                                                  |             |

| 6.2.5. Command line Assembler for 8051                                                                                                                 |             |

| 6.2.6. IDE Tool for Coding of 8051                                                                                                                     |             |

| 6.2.7. Simulation in ISIS                                                                                                                              |             |

| 6.3 EXPERIMENTAL PART                                                                                                                                  |             |

| 6.3.1. Installation of A51 to your work folder                                                                                                         |             |

| 6.3.2. Simulation of a Microcontroller Circuit                                                                                                         |             |

| 7. 8051 MEMORY DECODERS AND MEMORY INTERFACE                                                                                                           |             |

| 7.1 OBJECTIVE                                                                                                                                          | 55          |

| 7.2 8051 MEMORY INTERFACING                                                                                                                            |             |

| 7.3 EXPERIMENTAL PART                                                                                                                                  |             |

| 7.3.1. Installation of KC51 and preparation of HEX files                                                                                               |             |

| 7.3.2. Simulation of 8051 with External Memory                                                                                                         |             |

|                                                                                                                                                        |             |

| 8. 8051 MEMORY MAPPED I/O AND 8255A INTERFACING                                                                                                        |             |

| 8.1 Objective                                                                                                                                          |             |

| 8.2 8051 External IO Interfacing                                                                                                                       |             |

| 8.3 EXPERIMENTAL PART                                                                                                                                  |             |

| 8.3.1. Memory Mapped I/O interfacing                                                                                                                   |             |

| 8.3.2. Interfacing 8255 to 8051 Microcontroller.                                                                                                       |             |

| 8.3.3. Interfacing 8086 to a stepper Motor.                                                                                                            |             |

| 9. DESIGN AND CODING OF AN INTELLIGENT RESTAURANT SERVICE                                                                                              | ГЕRMINAL 69 |

| 9.1 OBJECTIVE                                                                                                                                          |             |

| 9.2 INTRODUCTION                                                                                                                                       |             |

| 9.2.1. Installing KC51 on your drive                                                                                                                   |             |

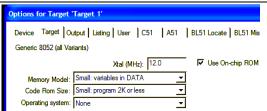

| 9.2.2. Starting a 8051 or 8052 project in KC51                                                                                                         | 69          |

| 9.2.3. LCD display                                                                                                                                     |             |

| 9.2.4. Serial Port                                                                                                                                     |             |

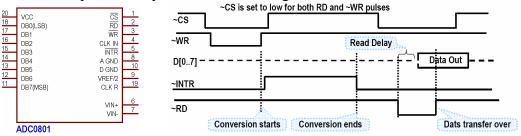

| 9.2.5. ADC interfacing                                                                                                                                 |             |

| 9.2.6. Switches and Operation of the System                                                                                                            |             |

| 9.3 ABOUT KEIL C51 COMPILER                                                                                                                            |             |

| 9.4 Design Requirements                                                                                                                                |             |

| 9.5 Reporting                                                                                                                                          | 77          |

| 10. DESIGN AND CODING OF AN INTELLIGENT HUMAN WEIGHT SCALE                                                                                             |             |

|                                                                                                                                                        | 70          |

|                                                                                                                                                        |             |

| 10.1 OBJECTIVE                                                                                                                                         |             |

| 10.2 INTRODUCTION                                                                                                                                      |             |

| 10.2 INTRODUCTION<br>10.2.1. Installing KC51 on your drive                                                                                             |             |

| 10.2       INTRODUCTION         10.2.1.       Installing KC51 on your drive         10.2.2.       Starting a project in KC51 for 8051 or 8052 projects |             |

| 10.2INTRODUCTION10.2.1.Installing KC51 on your drive10.2.2.Starting a project in KC51 for 8051 or 8052 projects10.2.3.LCD display                      |             |

| 10.2       INTRODUCTION         10.2.1.       Installing KC51 on your drive         10.2.2.       Starting a project in KC51 for 8051 or 8052 projects |             |

|           | Assemblers and Development Tools for 8086 and 8051 Microprocessors | vii |

|-----------|--------------------------------------------------------------------|-----|

| 10.       | 2.6. Switches and Operation of the System                          |     |

| 10.3      | ABOUT KEIL C51 COMPILER                                            |     |

| 10.4      | DESIGN REQUIREMENTS                                                | 80  |

| 10.5      | REPORTING                                                          |     |

| . APPI    | ENDIX                                                              | 8   |

| COMP      | LETE 8086 INSTRUCTION SET                                          |     |

|           |                                                                    |     |

|           | emonics                                                            |     |

|           |                                                                    |     |

| Op        | emonics<br>erand types:<br>es:                                     |     |

| Op<br>Not | erand types:                                                       |     |

# TASM, EDIT, DEBUG and Emu8086 Assembler Tools

# 1.1 Objective

**TASM** is one of the well known **8086** Assembler programs. This experiment will introduce you **TASM**, its input, and output file types.

Our objective covers hands-in experience to use

"Notepad" to create an assembler source file,

"TASM" to assemble the a source file into an object code

"TLink" to link an object code into an executable file.

"TD" and "Emu8086" debuggers to trace an executable file.

# 1.2 Introduction

Assembly language is the lowest level of symbolic programming for a computer system. It has several advantages and disadvantages over the higher level programming languages. Assembly language requires an understanding of the machine architecture, and provides huge flexibility in developing hardware/software interface programs such as interrupt service routines, and device drivers. **8086 Turbo Assembler** is one of the well known assembler programs used for PC-XT and AT family computers.

# 1.2.1. Editing the source file

The source for an assembly program is written into a text file with the extension -.ASM, in ASCII coding. Any ASCII text editor program can be used to write an assembly source file. We recommend to use **NOTEPAD** as a general purpose text editor, or the source editor of the **Emu86**, which is especially tailored to write **8086 Flat ASM** sources for your experiments.

# 1.2.2. Assembling to an object file

Once the source file is ready for assembling, you will need **TASM** program to be executed on the source file. **TASM** is a quite old program, written for **DOS** environment. Indeed, in most embedded system application DOS operating system is preferred over Windows because Windows is unnecessary, too bulky and too expensive for most embedded applications. In the **Windows** operating system, you

Environment.

can invoke a **DOS** command window by running the "**CMD.EXE**" executable. Figure 1 shows a Command Window, with its typical cursor. You may change the font and the colors of the Command window by the defaults and properties dialog which is opened with a left-click on the windows title. Colors such as screen text black on white, popup text blue on gray, and fonts Lucida-Console 18 point will make your command window much more readable. Whenever you want, you can use **CLS** command of DOS to clear the screen and the screen buffer.

The Turbo Assembler program (**TASM.EXE**) can be started in the command window by writing TASM <source-file-name>, and transmitting it to DOS using the"ENTER" key. The full syntax of TASM command is:

## >TASM [options] source [,object] [,listing] [,xref]

TASM command line options are shown in Table 1.

| Table 1. Possible Switches of the Turbo Assembler Program. |

|------------------------------------------------------------|

|------------------------------------------------------------|

|               | ressione switches of the furbe resembler frequent.       |

|---------------|----------------------------------------------------------|

| /a,/s         | Alphabetic or Source-code segment ordering               |

| /c            | Generate cross-reference in listing                      |

| /dSYM[=VAL]   | Define symbol SYM = 0, or = value VAL                    |

| /e,/r         | Emulated or Real floating-point instructions             |

| /h,/?         | Display this help screen                                 |

| /iPATH        | Search PATH for include files                            |

| /jCMD         | Jam in an assembler directive CMD (eg. /jIDEAL)          |

| /kh#,/ks#     | Hash table capacity #, String space capacity #           |

| /I,/Ia *      | Generate listing: I=normal listing, Ia=expanded listing  |

| /ml,/mx,/mu   | Case sensitivity on symbols: ml=all, mx=globals, mu=none |

| /n            | Suppress symbol tables in listing                        |

| /p            | Check for code segment overrides in protected mode       |

| /t            | Suppress messages if successful assembly                 |

| /w0,/w1,/w2   | Set warning level: w0=none, w1=w2=warnings on            |

| /w-xxx,/w+xxx | Disable (-) or enable (+) warning xxx                    |

| /x            | Include false conditionals in listing                    |

| /z            | Display source line with error message                   |

| /zi,/zd       | Debug info: zi=full, zd=line numbers only                |

In DOS and Assembly programming, the names are not case-dependent, which means writing TASM FIRST, Tasm first, tasm FIRST or tasm firST does not make any difference.

Assume that you have written the following simple assembly program into a text file with the name **first.asm**. To assemble it into **first.obj** file, you shall simply write the command

>tasm first

### 1.2.3. Linking to an Executable or Command File

The object files contains the program code but some of the labels are still in symbolic form. A linker converts them into the executable file replacing all symbols with their corresponding values. The use of library procedures, and splitting the large programs into modules are possible since a linker can calculate a label referred from a different object file. The file first.obj is converted to an executable by the DOS command

#### >tlink first

Figure 2 shows typical command window message after tasm and tlink is executed.

Assemblers And Development Tools For 8086 And 8051 Microprocessors

| G:\328\LNotes\First\cmd.exe                                                                               | - 🗆 ×    |

|-----------------------------------------------------------------------------------------------------------|----------|

| Microsoft Windows XP [Version 5.1.2600]<br>(C) Copyright 1985-2001 Microsoft Corp.                        | <u> </u> |

| G:\328\LNotes\First>tasm first<br>Turbo Assembler Version 1.0 Copyright (c) 1988 by Borland International |          |

| Assembling file: FIRST.ASM<br>Error messages: None<br>Warning messages: None<br>Remaining memory: 455k    |          |

| G:\328\LNotes\First>tlink first<br>Turbo Link Version 2.0 Copyright (c) 1987, 1988 Borland International  |          |

| G:\328\LNotes\First>                                                                                      |          |

Figure 2 Command Window after tasm and tlink are executed.

After running Tlink, you shall find the executable file **first.exe** in your working folder. First.exe terminates with a return to DOS interrupt, without giving any message. An assembly debugging tool can trace what happens during the execution of the first.exe file.

## 1.2.4. Tracing and Debugging of an EXE file

Turbo Debugger, **td.exe**, is an 8086 debugging tool which gives a convenient view of the CPU status, and the memory segments. The command line syntax of TD has options, program-file-name, and arguments

**>TD** [options] [program [arguments]] -x- = turn option x offThe options of td.exe is shown in Table 2.

Table 2. Command Line Options for Turbo Debugger TD.EXE

| -c <file></file> | Use configuration file <file></file>                            |

|------------------|-----------------------------------------------------------------|

| -do,-dp,-ds      | Screen updating: do=Other display, dp=Page flip, ds=Screen swap |

| -h,-?            | Display this help screen                                        |

| -i               | Allow process id switching                                      |

| -k               | Allow keystroke recording                                       |

| -                | Assembler startup                                               |

| -m<#>            | Set heap size to # kbytes                                       |

| -р               | Use mouse                                                       |

| -r               | Use remote debugging                                            |

| -rn <l;r></l;r>  | Debug on a network with local machine L and remote machine R    |

| -rp<#>           | Set COM # port for remote link                                  |

| -rs<#>           | Remote link speed: 1=slowest, 2=slow, 3=medium, 4=fast          |

| -SC              | No case checking on symbols                                     |

| -sd <dir></dir>  | Source file directory <dir></dir>                               |

| -sm<#>           | Set spare symbol memory to # Kbytes (max 256Kb)                 |

| -sn              | Don't load symbols                                              |

| -vg              | Complete graphics screen save                                   |

| -vn              | 43/50 line display not allowed                                  |

| -vp              | Enable EGA/VGA palette save                                     |

| -W               | Debug remote Windows program (must use -r as well)              |

| -y<#>            | Set overlay area size in Kb                                     |

| -ye<#>           | Set EMS overlay area size to # 16Kb pages                       |

3

| C: 000>B8735<br>C: 000>B8735<br>C: 0005 A0060<br>C: 0008 8ED8<br>C: 0005 A0060<br>C: 0005 A0060<br>C: 0005 A0060<br>C: 0005 A0060<br>C: 0005 A2080<br>C: 0011 B44C<br>C: 0015 00522<br>C: 0015 00522<br>C: 0018 0000<br>C: 001A 0000<br>C: 001A 0000 | 5B mov<br>mov<br>00 mov<br>0700 mov<br>add<br>00 mov<br>int<br>25 add<br>add           | ax,5873<br>ds,ax<br>al,[0006]<br>bl,[0007]<br>al,bl<br>[0008],al<br>ah,4C<br>21<br>[bp+si+25],d<br>[bx+si],al<br>[bx+si],al | es 5B62<br>ss 5B74                             | c=0<br>z=0<br>s=0<br>o=0<br>p=0<br>a=0<br>i=1<br>d=0 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|--|

| ds:0008 1D F0<br>ds:0010 13 22                                                                                                                                                                                                                       | add<br>add<br>) FF 9F 00 9A F<br>) E4 01 13 22 A<br>2 80 02 6E 1C D<br>2 01 00 02 FF F | E 01 ↔-õ©́‼"«©<br>C 0D ‼"Ç⊜n∟ <mark>_</mark> ♪                                                                              | cs 5B72<br>ip 0000<br>ss:0042 00<br>ss:0040►00 | 110                                                  |  |

Entering the command

#### >td first

into the command window will start the debugger to load the executable **first.exe** to its memory space. The screenshot of **TD** is shown in Figure 3. In Turbo debugger, you can execute the instructions step by step and trace the execution of the code. Any message written to the screen will invoke the screen display mode to let you observe the message.

### 1.2.5. Emu86 IDE

An Integrated Development Environment (IDE) provides a convenient environment to write a source file, assemble and link it to a -.COM or -.EXE file, and trace it in both source file, and machine code. Emu86 is an educational IDE for assembly program development. You can download the latest student version of EMU86 from the web page www.emu8086.com. It is a Windows program, and will run by dragging an -.ASM, -.OBJ, -.LST, -.EXE , or -.COM file into the emu86 shortcut icon. By this action, asm or 1st files will start the 8086 assembler source editor, while obj and exe files starts the disassembler and debugger units.

### 1.2.6. EMU8086 Source Editor

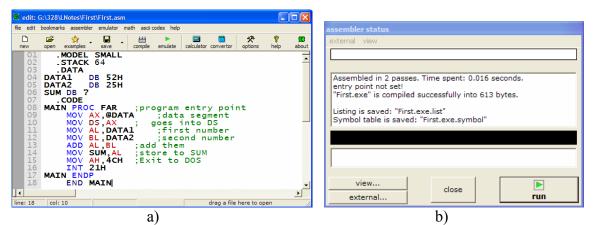

The source editor of EMU86 is a special purpose editor which identifies the 8086 mnemonics, hexadecimal numbers and labels by different colors as seen in Figure 4.

Figure 4. a) EMU8086 Source Editor, and b) assembler status report windows.

The compile button on the taskbar starts assembling and linking of the source file. A report window is opened after the assembling process is completed. Figure 5 shows the emulator of 8086 which gets opened by clicking on emulate button.

|       | emu      | Ilato   | r: Fi | rst. | exe_             |      |            |                   |            |                     |      |            |       |               |       |   |  | _ 0 | X |

|-------|----------|---------|-------|------|------------------|------|------------|-------------------|------------|---------------------|------|------------|-------|---------------|-------|---|--|-----|---|

| file  | ma       | th d    | ebug  | vie  | ew e             | xter | nal v      | irtual d          | evices     | virtual dri         | ve h | nelp       |       |               |       |   |  |     |   |

|       | Loa      |         |       |      | <b>)</b><br>load |      | ste        | <b>( </b><br>back | sin        | gle step            |      | ><br>run   | 1.12  | ep delay      |       |   |  |     |   |

| re re | egiste   | rs<br>H | L     |      |                  | Г    | 071        | 5:000             | 90         |                     |      | Γ          | 0715: | 0000          |       |   |  |     |   |

|       | AX       | 00      | 00    |      |                  |      | 50:        |                   | 184        |                     | -    |            |       | 0071          | 4h    |   |  |     | - |

|       | ВX       | 00      | 00    |      |                  |      | 51:<br>52: | 14<br>07          | 020        |                     |      |            | DS,   | AX<br>[000]   | 0061  |   |  |     |   |

|       | cx       | 00      | 65    |      | 0                |      | 53:        | 8F                | 142        |                     |      |            |       | [000          |       |   |  |     |   |

|       | DX       | 00      | 00    |      | 0                | -    | 54:        | D8                |            | _                   |      | ADD        | AL,   | BL            |       |   |  |     |   |

|       | CS       | 07      | 15    |      |                  | -    | 55:<br>56: | A0<br>00          |            |                     |      |            |       | 002h]<br>04Ch |       |   |  |     |   |

|       | IP       |         | 00    |      | ŏ                | 71   | 57:        | 00                |            |                     |      |            | 021   |               |       |   |  |     |   |

|       | SS       |         | 10    |      | 0                |      | 58:        |                   | 138        |                     |      | NOP        |       |               |       |   |  |     |   |

|       | SP       | -       | 40    |      |                  |      | 59:<br>54· | 1E<br>01          | 030        |                     |      | NOP        |       |               |       |   |  |     |   |

|       | BP       |         | 00    |      | ŏ                |      | 5B:        | 00                | 000        | NUL                 |      | NOP        |       |               |       |   |  |     |   |

|       | SI       | _       | 00    |      |                  |      | 5C:        | 02                |            | Ū                   |      | NOP        |       |               |       |   |  |     |   |

|       | oi<br>DI | 1       | 00    |      |                  | -    | 5D:<br>5F: | C3<br>A2          | 195<br>162 |                     |      | NOP<br>NOP |       |               |       |   |  |     |   |

|       |          | -       | 00    |      |                  |      | 5F:        |                   |            |                     |      |            |       |               |       |   |  |     | - |

|       | DS       | _       |       |      |                  |      |            | 1011              |            | - 6008 - 1 <u>0</u> |      | 10.5.635   |       | 244           | -     | - |  |     | - |

|       | ES       | 07      | 00    |      | sci              | een  | so         | urce              | reset      | aux                 |      | vars       | debug | stack         | flags |   |  |     |   |

Figure 5. first.exe in the emulator window of EMU8086 debugging environment Emul8086 environment contains templates to generate command and executable files. Another benefit of Emul8086 is its emulation of a complete system, including the floppy disk, memory, CPU, and I/O ports, which raises opportunity to write custom bios and boot programs together with all other coding of a system. More over, its help is quite useful even for a beginner of **asm** programming.

### 1.2.7. EMU8086 / MASM / TASM compatibility

Syntax of emu8086 is fully compatible with all major assemblers including *MASM* and *TASM*; though some directives are unique to this assembler.

1) If required to compile using any other assembler you may need to comment out these directives, and any other directives that start with a '#' sign:

```

#make_bin#

#make_boot#

#cs=...#

etc...

```

2) Emu8086 ignores the ASSUME directive. manual attachment of CS:, DS:, ES: or SS: segment prefixes is preferred, and required by emu8086 when data is in segment other then DS. for example:

| mov | ah, | [bx]    | ; | read | byte | from | DS:BX |

|-----|-----|---------|---|------|------|------|-------|

| mov | ah, | ēs:[bx] | ; | read | byte | from | ES:BX |

3) emu8086 does not require to define segment when you compile segmentless COM file, however MASM and TASM may require this, for example:

| CSEG<br>ORG 100 | SEGMENT                                                          | ; code segment starts here.                                        |

|-----------------|------------------------------------------------------------------|--------------------------------------------------------------------|

|                 | MOV AL, 5<br>MOV BL, 2<br>XOR AL, BL<br>XOR BL, AL<br>XOR AL, BL | ; some sample code                                                 |

| CSEG<br>END     | RET<br>ENDS<br>start                                             | ; code segment ends here.<br>; stop compiler, and set entry point. |

- 4) entry point for COM file should always be at 0100h, however in MASM and TASM you may need to manually set an entry point using END directive even if there is no way to set it to some other location. emu8086 works just fine, with or without it; however error message is generated if entry point is set but it is not 100h (the starting offset for com executable). the entry point of com files is always the first byte.

- 5) if you compile this code with Microsoft Assembler or with Borland Turbo Assembler, you should get *test.com* file (11 bytes). Right click it and select send to and emu8086. You can see that the disassembled code doesn't contain any directives and it is identical to code that emu8086 produces even without all those tricky directives.

- 6) emu8086 has almost 100% compatibility with other similar 16 bit assemblers. the code that is assembled by emu8086 can easily be assembled with other assemblers such as TASM or MASM, however not every code that assembles by TASM or MASM can be assembled by emu8086.

- 7) a template used by emu8086 to create **EXE** files is fully compatible with *MASM* and *TASM*.

- 8) The majority of **EXE** files produced by *MASM* are identical to those produced by *emu8086*. However, it may not be exactly the same as TASM's executables because *TASM* does not calculate the checksum, and has slightly different EXE file structure, but in general it produces quite the same machine code. There are several ways to encode the same machine instructions for the 8086 CPU, so generated machine code may vary when compiled on different compilers.

- 9) Emu8086 integrated assembler supports shorter versions of **byte ptr** and **word ptr**, these are: **b.** and **w.** For *MASM* and *TASM* you have to replace **w.** and **w.** with **byte ptr** and **word ptr** accordingly.

```

for example:

lea bx, var1

mov word ptr [bx], 1234h ; works everywhere.

mov w.[bx], 1234h ; same instruction / shorter emu8086

syntax.

hlt

var1 db 0

var2 db 0

```

10) LABEL directive may not be supported by all assemblers, for example: **TEST1 LABEL BYTE**

```

; ...

LEA DX,TEST1

```

the above code should be replaced with this alternative construction: **TEST1**:

```

: ..

```

```

MOV DX, TEST1

```

the offset of TEST1 is loaded into DX register. this solutions works for the majority of leading assemblers.

6

#### 1.3 Experimental Part

In this experiment you will use TASM, TLINK, and EMU8086 to generate an executable from an assembly source, and to trace the step-by-step execution of the executable in TD debugger and in EMU8086 emulator

#### 1.3.1. Writing a Source File

**Objective:** to practice writing and editing an ASCII assembly source file using notepad. **Procedure:** Generate a folder asm. Copy the files tasm.exe, tlink.exe, td.exe into asm folder. Generate a working folder with name **exp1**, and start a text file in your working folder In the explorer while folder is open

- click on right button of mouse, and

- select new, select text document. "New Text Document.txt" will be generated.

- Rename it "expl.asm"

Now, you have an empty text file, with the name expl.asm. Use windows-start > allprograms > accessories > notepad to open the Notepad text editor. Drag the file expl.asm to the title-bar of the Notepad. The title will change to expl.asm – Notepad. It means that you successfully opened the file expl.asm for editing in notepad. Write the following source program into the edit window.

-----file: exp1.asm-----STUDENT NAME and SURNAME: STUDENT NUMBER: TITLE PROG2-2 (EXE) PURPOSE :ADD 4 WORDS OF DATA PAGE 60,132 .MODEL SMALL .STACK 64 \_\_\_\_\_ .DATA DW 234DH, 1DE6H, 3BC7H, 566AH DATA\_IN ORG 10H DW ? SUM \_\_\_\_\_ : . CODE ;THIS IS THE PROGRAM ENTRY POINT MAIN PROC FAR AX, @DATA ; load the data segment adress MOV ;assign value to DS ;set up loop counter CX=4 MOV DS,AX CX,04 MOV DI, OFFSET DATA\_IN ; set up data pointer DI MOV SI,OFFSET SUM BX,00 MOV ;initialize BX MOV ADD\_LP: ;add contents pointed at by [DI] to BX ;increment DI twice ADD BX,[DI] INC DI ;to point to next word INC DI ;decrement loop counter DEC CX ;jump if loop counter not zero ADD\_LP JNZ SI,OFFSET SUM MOV ; SI points SUM ;store BX to SUM in data segment MOV [SI],BX MOV ĀH, 4CH ;set up return INT 21H ;return to DOS MAIN ENDP END MAIN :this is the program exit point -----end of file -----

Use tabs to start the mnemonics at the same column.

#### **Reporting:**

Start a text file (you may use *notepad*) with name **exp1.txt**. Fill in the following title to your text file.

```

CMPE 323 Experiment-1 Report. <your name surname, student number>

PART1 Assembly source file

Copy-and-paste your expl.asm into your report file.

; STUDENT NAME and SURNAME: ALI VELI

; STUDENT NUMBER: 012345

TITLE PROG2-2 (EXE) PURPOSE :ADD 4 WORDS OF DATA

PAGE 60,132

.MODEL SMALL

...

```

Keep your report file in a safe place until you complete the experiment and e-mail it to the specified address.

### 1.3.2. Assembling with TASM

**Objective:** Assembling the source file with TASM, and tracing it in TD. **Procedure:** You have already written the source file **exp1.exe**.

- Organize a folder structure such as

ASM folder contains

files TASM.EXE, TLINK.EXE, and TD.EXE.

#### folder exp1, which contains exp1.asm and exp1.bat.

-Edit **exp1.asm** to contain the complete source text by copy and paste. Fill your student name and number to the first two lines.

-Edit exp1.bat to have the following text lines in it.

```

..\tasm -l exp1

pause

..\tlink exp1

pause

..\td exp1

pause

```

- -Click on exp1.bat to execute assembler. You will observe a DOS window opened, and tasm executed on exp1.asm, with the list option active. DOS window will pause and will allow you to read the messages generated by TASM. You will observe exp1.obj, exp1.lst, and exp1.map files generated in folder exp1.

- -If you press on space-bar, bat file will continue to execution, and it will execute the linker tlink on **exp1.obj**. Tlink will generate **exp1.exe** file into the **exp1** folder. Batch file will pause until you press the space-bar.

- -Press the space-bar again to execute turbo debugger on **exp1.exe** file. In the debugger, you can trace the execution by executing each line of the assembly program stepwise.

#### **Reporting:**

In td read the hexadecimal contents of the program code expl.exe (28 bytes), and the contents of the memory location cs:0009. Start PART2 in your report file, and fill in (as text, i.e., A3 02 etc)

A3 U2 elc) PART2 B8 68 5B 8E D8 ... cs:0009 contains ....

Then open expl.lst, which is generated by turbo assembler in a text editor (notepad). Copy-and-paste the first page of the listing into your report file

| expl.lst contains<br>Turbo Assembler Version 1.0<br>EXPl.ASM | 01/13/11 11:32:32                          | Page 1 |

|--------------------------------------------------------------|--------------------------------------------|--------|

| 1                                                            | ; STUDENT NAME and SU<br>; STUDENT NUMBER: | RNAME: |

| 3<br>4 0000                                                  | .MODEL SMALL                               |        |

Assemblers And Development Tools For 8086 And 8051 Microprocessors

| 5 0000             |                     | .STACK 64                                                |

|--------------------|---------------------|----------------------------------------------------------|

| 7 0000             | 2245 1556 2557 566  | , DATA                                                   |

| 8 0000<br>9        | 234D 1DE6 3BC7 566A | DATA_IN DW 234DH,1DE6H,3BC7H,566AH<br>ORG 10H            |

| 10 0010            | ????                | SUM DW ?                                                 |

| 12 0012<br>13 0000 |                     | '.CODE<br>MAIN PROC FAR ;THIS IS THE PROGRAM ENTRY POINT |

| 14 0000            | B8 0000s            | MOV AX,@DATA ;load the data segment address              |

|                    |                     |                                                          |

Save your report file in a safe place until you complete the experiment and e-mail it to the specified address.

#### 1.3.3. Assembling with Emu8086

**Objective:** Assembling a source file with Emu8086 assembler/emulator

#### **Procedure:**

- -Start Emu8086, and close the welcome window. Use "open" in taskbar to start the file browser. Select the folder exp1, and open exp1.asm.

- -Emu8086 cannot use title, page, and org directives. Put a semicolon to make them a comment line. Then, use emulate in taskbar to assemble, and start the emulator window with the **exp1.exe**.

-Use the taskbar-button "single step" to execute each line of the assembly source.

#### Reporting

In **PART3** of your report answer the following questions in full sentences.

- a) How many times the loop passes through the **add** instruction?

- b) What is the effective address of the **add** instruction in the code segment?

After completing the experiment, write an e-mail that contains Please find the attached report file of experiment 1. Regards. 012345 Ali Veli

attach the report file to the e-mail and send it

- from your student-e-mail account

- to the e-mail address cmpe323lab@gmail.com

- with the subject: "exp1".

Late and early deliveries will have 20% discount in grading. No excuse acceptable.

Assemblers and Development Tools for 8086 and 8051 Microprocessors

# **2.** Data Types, and Effect of ALU instructions on Flags

# 2.1 Objective

The aim of this experiment consists of

i- Experimenting with data types, and assembler directives.

ii- Observing the effect of ALU instructions on flags.

iii- Exercising some DOS interrupt services.

# 2.2 Preliminary Study

Before attending the lab, study from Mazidi&Mazidi textbook

- Section 1.4 and 2.5 to understand the data types and directives.

- Section 1.3, 1.4, and 1.5 to understand the MOV and ADD instructions, and the flags.

# 2.3 Experimental Part

# 2.3.1. Data types and Data directives

**Objective:** to observe the coding of several data types in various formats. **Procedure-1:**

- Organize a folder structure such as

ASM folder contains

files TASM.EXE, TLINK.EXE, and TD.EXE.

folder exp2, which contains exp2p1.asm and exp2p1.bat.

-Edit exp2p1.asm to contain the following source text by copy and paste.

Fill your student name and number to the first two data items.

```

---file exp2p1.asm-----

.mode1 smal1

.stack 64

.data

data1 db

'Name-Surname'

data2 db

data3 db

'Number'

45, 4Ch

0123, 0123h

3, 2 dup(5)

'Hello world! $'

data4 dw

data5 dd

data8 db

.code

mov ax,@data

mov ds,ax

mov ds,ax

mov dx,offset data8

mov ah,9

int 21h

displays message

mov ah,4ch

int 21h ; return to dos

end

-----end of file-----

```

In this program, **data8** is a DOS screen message, and all DOS screen messages shall terminate with a "\$" character. **data8** contains the ASCII message string to be printed on the screen. **mov dx,offset data8** loads the offset of **data8** in

ds into dx. mov ah,09h determines "print the pointed string to the screen" service among many other DOS int 21h services. Similarly, ah=4ch selects "exit to DOS" service among many int 21h DOS services.

- exp2p1.bat should have the following text lines in it.

```

..\tasm -l exp2p1

pause

..\tlink exp2p1

pause

exp2p1

pause

```

- Execute the batch file, and press space bar to proceed with **tlink** and **exp2p1**. You will observe the message "Hello world" written on the dos command window before pressing the space bar for the third pause.

- Open the **exp2p1.lst** file in notepad to observe how the data directives place the data items into the reserved memory locations in the data segment (First start notepad, then open the file from browser, or drag the file into notepad window). You will observe the followings in the list file.

#### **Observations-1:**

1- The quoted strings are converted to ASCII coding. Check the coded characters against the following printable ASCII character table.

|    | -0 | -1 | -2 | -3 | -4 | -5 | -6 | -7 | -8 | -9 | -A | -B | -C                                                                                                                                                 | -D     | -E         | -F |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|----|

| 2- |    | !  | "  | #  | \$ | %  | &  | I  | (  | )  | *  | +  | ,                                                                                                                                                  | I      |            | /  |

| 3- | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | :  | ;  | <                                                                                                                                                  | II     | >          | ?  |

| 4- | 0  | Α  | В  | С  | D  | Ε  | F  | G  | Η  | Ι  | J  | Κ  | L                                                                                                                                                  | Μ      | Ν          | 0  |

| 5- | Ρ  | Q  | R  | S  | Т  | U  | V  | W  | Х  | Υ  | Ζ  | [  | $\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{$ |        | ^          | I  |

| 6- |    | a  | b  | С  | d  | е  | f  | g  | h  | i  | j  | k  | 1                                                                                                                                                  | m      | n          | 0  |

| 7- | р  | q  | r  | S  | t  | u  | V  | W  | X  | У  | Ζ  | {  |                                                                                                                                                    | $\sim$ | $\uparrow$ | ↓  |

2- db directive codes the numbers in single bytes, in the listed order.

- 3- dw directive codes the numbers in two-byte groups, in little endian convention.

- 4- dd codes the numbers in four-byte groups, in little endian convention.

- 5- **dup()** codes repeated number of data into data area. In the list file data is shown by dup() function. However, sufficient number of bytes are allocated for the duplicate data.

#### **Reporting:**

- 1- Start a text file with the name **exp2.txt**.

- 2- Write the Report Title in the following format

```

CMPE328 Experiment 2, Report file by <name surname studentnr> Part 1 % \left( {\left( {n_{\rm s}} \right)^2 } \right)

```

- 2- Copy the data definition lines (data1 ... data8) from lst file to exp2.txt.

- 3- Save the text file to report the coming report item.

#### **Procedure-2:**

- 1- Open exp2p1.exe in td (i.e., first start td.exe, then open the file exp2p1.exe in td).

- 2- Right click on **ds**, and change its contents to the immediate value of the first instruction in the code segment (i.e, for **mov ax,5B68** make ds=5B68h.)

- 3- Click on **view > dump** to open the data segment window.

- 4- Right click on command window title-bar. From the pop-up menu click editmark.

- 5- Drag the mouse while left-clicked on data-segment dump window, to mark the ds- dump from your name to hello world message (including both lines as well).

- 6- While the marked area stays on the dump window, right-click on command window title-bar, and click **edit-copy** in the pop-up window. Then open **exp2.txt** in notepad, and use paste to transfer the copied text into **exp2.txt**. Your text will be similar to the following, however it will be different in some fields and addresses.

#### Typical exp2.txt file after Procedure-2, step-6 CMPE328 Experiment 2, Report file by <name surname studentnr> Part 1 4 0000 4E 61 6D 65 2D 53 75 + data1 db 'Name-Surname' 72 6E 61 6D 65 4E 75 6D 62 65 72 6 000C data2 db 'Number' 2D 4C 45, 4Ch 0123, 0123h 7 0012 data3 db 007B 0123 00000003 02\* (00000005) 8 0014 data4 dw 9 0018 + data5 dd 3, 2 dup(5) 10 48 65 6C 6C 6F 20 77 + data8 db 6F 72 6C 64 21 20 24 11 004A 'Hello world! \$' 12 ds:0000 4E 61 6D 65 2D 53 75 72 Name-Sur ds:0008 6E 61 6D 65 4E 75 6D 62 nameNumb er-L{ #? ds:0010 65 72 2D 4C 7B 00 23 01 ds:0018 03 00 00 00 05 00 00 00 23 01 ds:0020 05 00 00 00 03 00 00 00 ? ? ds:0028 00 00 00 00 14 31 82 00 ¶1é ds:0030 00 00 00 00 00 00 00 21 00 ds:0038 00 00 00 00 00 00 00 00 00 ds:0040 00 00 00 00 00 00 00 00 00 ds:0048 00 00 48 65 6C 6C 6F 20 Hello ds:0050 77 6F 72 6C 64 21 20 24 world! \$

Save exp2.txt, and observe the following items on the edit window.

### **Observations-2:**

- 1- data3 db 45, 4ch is expressed in 1st file memory listing by 2D 4c (45=2Dh).

- 2- data4 dw 0123, 0123h is converted to 007B 0123 in the lst file, but it is written in little endian convention into the memory area as 7B 00 23 01 (shown in circles).

- 3- data5 dd 3, 2 dup(5) is expressed in 1st file by 00000003 02\*(00000005), but it is filled into memory as 03 00 00 00 05 00 00 05 00 00 00 (in littleendian double-words, and 5 repeated twice.)

## 2.3.2. ALU Operations and Flags

Objective is to observe the changes of flags with the add, sub, cmp, inc, dec, and, or, neg, mov instructions.

#### **Procedure:**

- In this experiment you will use Emu8086 emulator.

- Take your list of instructions from your assistant. The list will contain **add**, **sub**, **cmp**, **inc**, **dec**, **and**, **or**, **neg**, and **mov** instructions with immediate and register addressing modes.

- Start Emu8086 emulator. Close the welcome window. Open the file **exp2p1.asm.** Use Save-as to save it with the name **exp2p2.asm**.

- Emu8086 does not allow some data directives. Place a semicolon before **data6** and **data7** to get rid of **dq** and **dt** directives.

- Insert the code you've taken from your assistant after the **mov ds,ax** line.

- Emulate the assembler code by clicking on Emulate toolbar-button.

- In the emulator window, click on flags-button to open the flags-window.

**Reporting:** Use single-step button to execute each instruction. For each executed instruction in your list, fill in the flag status into the report file **exp2.txt**. i.e.. Part 2

| Part 2  |         |      |        | AX and Flags you read af     |

|---------|---------|------|--------|------------------------------|

|         |         | AX   | CZSOPA | the instruction is executed. |

| mov ax, | ,08803h | 8803 | 000000 |                              |

| add ax, | ,07654h | FE57 | 001000 |                              |

| sub ax, | ,0F803h | 0654 | 000000 |                              |

| or ax,  | 0F000h  | F654 | 001000 |                              |

| and ax, |         | 0004 | 000000 |                              |

| mov ax, | ,0FFFFh | FFFF | 000000 |                              |

| inc ax  |         | 0000 | 010011 |                              |

| dec ax  |         | FFFF | 001011 |                              |

| add ax, | ,1      | 0000 | 110011 |                              |

| sub ax, |         | FFFF | 101011 |                              |

| sub ax, | ,08000h | 7fff | 000010 |                              |

| cmp ax, | ,07000h | 7fff | 000010 |                              |

| cmp ax, | ,09000h | 7fff | 101110 |                              |

|         |         |      |        |                              |

|         |         |      |        |                              |

You shall observe

- 1- mov instructions never change any flags,

- 2- inc, and dec never change carry flag,

- 3- an immediate **sub** can do same job with **inc**, but it effects carry, and its code takes 2-bytes longer than **dec**.

- 4- The flags changed by each instruction is given in the 80386 instruction sheet.

add, sub, neg, cmp determine flags CZSOPA ;

inc, dec determine flags ZSOPA ;

and, or determine flags CZSOP ;

mov does not change any flag (it is not an ALU operation)

The flags affected by each instruction is listed in 80x86-instruction-set table.

After you complete the procedures, please save and close **exp2.txt** file, and e-mail it using your student e-mail account to cmpe323lab@gmail.com with the subject line "**exp2**" within the same day before the midnight.

#### Late and early deliveries will have 20% discount in grading. No excuse acceptable.

#### Free time practice:

Modify the program exp2p1.asm to replace mov dx,offset data8 with the instruction mov dx,offset data1.

What do you expect to be printed on the display?

What does it display when you run the assembled exe file?

What shall you do to display only your name-surname?

# 3.

# Simple Virtual 8086 Development Board

# 3.1 Objective

This experiment includes introduction to design of a virtual simple educational 8086 development board (VSED board) with simple digital i/o ports, and a UART-terminal connection. Our experimental part aims to give concepts of input and output ports with a hands on practice for verification of an executable code on a virtual simple educational 8086 system.

# 3.2 Introduction

## 3.2.1. 8086 and main memory

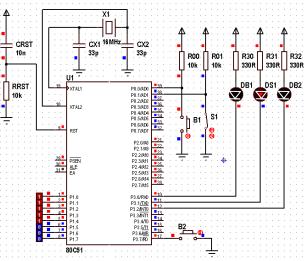

Virtual Simulation Model (VSM) samples in ISIS provide 8086 simulation that loads exe files to its internal memory. The executable files may be produced using any 8086 compiler including C or 8086 Assembler tools.

# 3.2.2. 8086 Processor Bus

ISIS provides a virtual simulation model (VSM) of 8086 including the 8086 processor bus. The simulation model provided by ISIS contains configurable internal memory which simplifies simulation of 8086 systems.

|                                                                          | U1                |                                                                                       |                                             |

|--------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------|---------------------------------------------|

| 21<br>22<br>24<br>18<br>31<br>30<br>23<br>0<br>23<br>0<br>17<br>33<br>19 | CLK               | AD[015]<br>A[1619]<br>ALE/QS0<br>BHE<br>DT/R/S1<br>DEN/S2<br>RD<br>WR/LOCK<br>M/IO/S0 | 25<br>34<br>27<br>26<br>32<br>0<br>29<br>28 |

|                                                                          | 8086<br>LOAD_SEG= | 0x0800                                                                                |                                             |

**Figure 1.** 8086 processor of Prosis 7.7. It contains internal memory which is configured by properties.

Bus is suitable for memory and IO interfacing. In this experiment, we plan to use it for IO interfacing.

#### 3.2.3. Address Latching

8086 has AD0-AD15 multiplexed address lines which transfers both data and address signals. Address is valid while ALE is high, and data is valid while ALE is low and either ~RD or ~WR line is low. 74237 octal latches are suitable for address latching purpose.

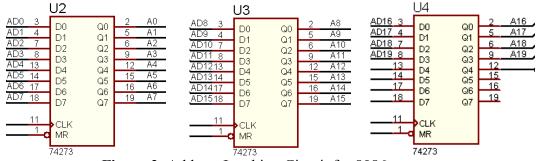

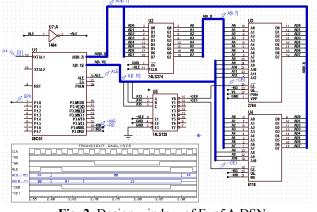

Figure 2. Address Latching Circuit for 8086 system.

CLK lines of U2, U3 and U4 are connected to ~ALE, which is obtained by inverting the ALE output (pin25) of the 8086 processor. MR is clear input of 74273 (memory reset) and all MR inputs are connected to high (Vss). The latch outputs A0 ... A19 are the buffered address bus of the system. AD0 ... AD15 are the unbuffered data lines of the 8086 system, and directly connected to the IO ports.

### 3.2.4. System Configuration

SED system has internal 64 k byte memory integrated into the 8086 device, starting from address 0x00800. The executable file shall be compiled in small model, and include its stack, data and code within the 64k memory range. The data, control and buffered address bus of 8086 is utilized to access to an 8-bit output port, two 8-bit input ports, and a universal serial asynchronous receiver transmitter (USART) unit.

### 3.2.5. IO Address decoding

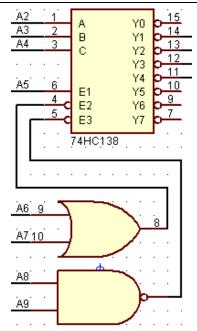

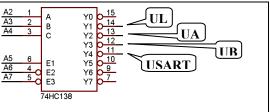

A 74HC138 provides address decoding for the chip select signals of these IO devices.

Figure 3. The IO address decoder of Small Educational Development System

The  $\sim$ E3 input of 74138 (3 to 8 line decoder) gets enabled only during IO-read an IO-write bus cycles of the 8086 processor. The buffered address lines A6, A5, A4, A3, and A2 are used for enable and select inputs of the decoder. Consequently the decoding map of the decoder is obtained in Table 1.

| -  |    |    |    |    |    |    |    |          |                             |  |  |  |  |  |

|----|----|----|----|----|----|----|----|----------|-----------------------------|--|--|--|--|--|

| A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 |          |                             |  |  |  |  |  |

| E  | 3  | E  | 2  | E1 | С  | В  | Α  | ~Y0 ~Y7  | Enabled output              |  |  |  |  |  |

| X  | Х  | X  | Х  | 0  | X  | X  | X  | ННННННН  | none                        |  |  |  |  |  |

| X  | X  | X  | 1  | X  | X  | X  | X  | ННННННН  | none                        |  |  |  |  |  |

| X  | X  | 1  | X  | X  | X  | X  | X  | ННННННН  | none                        |  |  |  |  |  |

| 0  | X  | X  | X  | X  | X  | X  | X  | ННННННН  | none                        |  |  |  |  |  |

| X  | 0  | X  | Х  | X  | X  | X  | X  | ННННННН  | none                        |  |  |  |  |  |

| 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | ГНННННН  | $\sim$ Y0 – not connected   |  |  |  |  |  |

| 1  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | НГННННН  | ~Y1 – output port UL        |  |  |  |  |  |

| 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | ННГНННН  | $\sim$ Y2 – input port – UA |  |  |  |  |  |

| 1  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | НННГННН  | ~Y3 – input port – UB       |  |  |  |  |  |

| 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | HHHHLHHH | ~Y4-USART                   |  |  |  |  |  |

| 1  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | ННННННН  | $\sim$ Y5 – not connected   |  |  |  |  |  |

| 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | НННННЦН  | $\sim$ Y6 – not connected   |  |  |  |  |  |

| 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | HHHHHHL  | $\sim$ Y7 – not connected   |  |  |  |  |  |

| 1  | 1  | X  | 1  | Х  | X  | X  | X  | ННННННН  | none                        |  |  |  |  |  |

Table 1. Address decoding map for 74138 decoder.

Thus, the 8-bit address map of Enable signals are given in Table 2.

| A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | hex         | port  |  |  |  |  |

|----|----|----|----|----|----|----|----|----|----|-------------|-------|--|--|--|--|

| 1  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | Х  | Х  | 324h - 327h | UL    |  |  |  |  |

| 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | Х  | Х  | 328h – 32Bh | UA    |  |  |  |  |

| 1  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | Х  | Х  | 32Ch – 32Fh | UB    |  |  |  |  |

| 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | Х  | Х  | 330h - 333h | USART |  |  |  |  |

Table 2. IO Port Addresses

For each IO device the first address of the address ranges are used to address the device conveniently. Simply, 324h is the address of UL, 328h and 32C are the addresses for UA

and UB. We will consider the USART address later since it has two internal registers namely control and data.

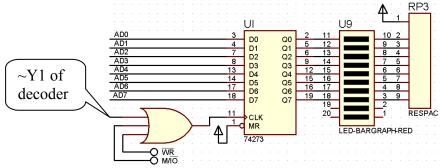

### 3.2.6. Simple Output Port UL

The output port UL is constructed using 74273 octal D-flip-flops with common clear ( $\sim$ MR) and common clock (CLK) inputs.  $\sim$ MR is permanently disabled by connecting it to high. The active low enable output  $\sim$ Y1 of the address decoder and the active low write output of 8086 are connected to the CLK input of the port through a NOR gate to enable the clock (with a high) when both  $\sim$ WR and  $\sim$ Y1 are low.

In the program we use the instructions

mov DX,324h

out DX,AL

to output the contents of AL to output port UL.

Figure 4. Simple isolated output port at address 24h installed with LED displays.

The outputs of the 74273 D-flip-flops are connected to digital LED array to display the output status in a convenient form. Note that the LED indicators glow while the latch outputs are high. For example, with the instructions

mov DX,324h mov AL, 03h out DX, AL

After the execution of the code LEDs of Q0 and Q1 shall remain dark, and Q3, Q4, Q5, Q6, and Q7 shall start to glow.

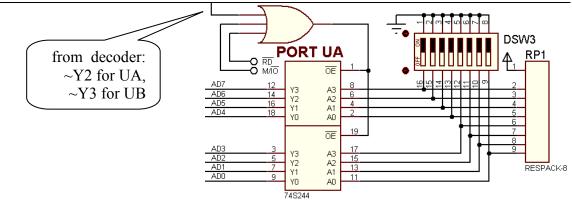

### 3.2.7. Simple Input Ports UA and UB

Input Ports UA and UB are designed to read the 8-bit dip-switch status into register AL. The instructions

```

mov DX,328h

in AL,DX

```

and

mov DX, 32Ch in AL, DX read the status of the switches SW1 and SW2 into AL.

Figure 5. Simple isolated input port at address 328h and 32Ch installed with switch array.

For example, if the switch positions of SW1 were set to On, On, On, Off, On, On, Off, On (in the order from 1 to 8) and the instruction in AL,28h was executed the corresponding bit of AL for On position contains 0, and for Off position it will be 1, resulting in AL=12h.

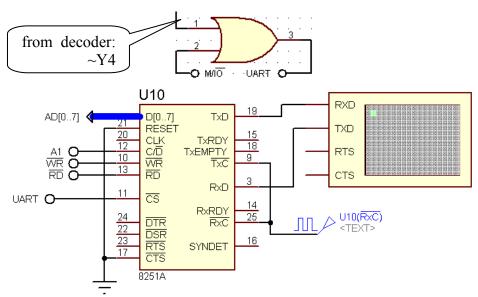

# 3.2.8. Serial Communication Device

The USART 8251A is enabled by  $\sim$ Y4 of the address decoder, and additionally it has a Control/ $\sim$ Data select line which is connected to A1. Moreover, the  $\sim$ RD and  $\sim$ WR lines provide reading and writing to control and data registers

Consequently it has the following address mapping

| A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | In/Out | hex address | addressed port |

|----|----|----|----|----|----|----|----|----|----|--------|-------------|----------------|

| 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | Х  | Out    | 330h - 331h | USART data out |

| 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | Х  | In     | 330h - 331h | USART data in  |

| 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | Х  | Out    | 332h - 333h | USART control  |

| 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | Х  | In     | 332h - 333h | USART status   |

USART has configuration registers which needs initialization. The Reset sequence of the USART provides safe reset of the device under the control of program.

```

mov DX, 332h

out DX, AL

out DX, AL

out DX, AL

mov AL, 40h

out DX, AL

; After reset sequence, USART expects the mode control,

: 8251 Mode=sdppbbmm,

async mode << sd=00,

no parity << pp=00;

data-bits: 5<<bb=00; 6<<bb=01; 7<<bb=10; 8<<bb=11;</pre>

baud rate factor: x1<<mm=01; x16<<mm=10; x64<<mm=11;</pre>

; mode8251 8-bit, no parity, baud=clock x1

mov AL, ODh

out DX, AL

; Next, USART waits command control

; 8251 Command = hmrtRdT

search SYN char: disable<<h=0 (async mode); enable<<h=1</pre>

internal reset: reset (expects mode) << m=1; command << m=0;</pre>

request to send: forces RTS low << r=1;

error reset : resets all error flags << r=1;

forces TxD low << t=1;

send break:

receive enable: enable << R=1;

data terminal ready: forces DTR low << d=1</pre>

transmit enable: enable << T=1;

mov

AL. 37h

; comd8251 both RC & TX, reset errors, RTS, DTR

active

```

out DX, AL

out DX,AL

After this initialization code, USART is ready to transmit characters by putting them into data-out register. It is possible to poll the status register to check the data-out and data-in registers are full or empty. User may get the received character from data-in register when bit-1 of status register is high, and may write the character to be transmitted into the data-out if bit-0 of the status register is high.

```

; This code reads received character into AL.

; If no character received then AL returns zero.

mov DX,332h

; status/control address

in AL, DX

; read status register

; zero flag is set if AL .AND. 01h is nonzero

test AL,01h

jz NotReceived

mov DX,330h

; data-in/data-out address

; read received bits from data-in into AL.

in AL, DX

; Purge out the start bit, remaining bits are data.

shr AL,1

NotReceived:

; Any code that process the received character shall be placed here.

Data transmission through USART is obtained by writing character into data-out register

after USART unit is ready for transmission of a character

; this code transmits the contents of AH register to USART.

WaitReady:

; status/control address

mov DX,332h

in AL, DX

; read status register

test AL,02h

; zero flag is set if AL .AND. 02h is nonzero

jz WaitReady

; Wait until flag is set

mov AL,AH

mov DX,330h

; data-in/data-out address

```

; received character transferred into AL.

In most applications serial io is managed through an input and an output buffer. USART generates an interrupt request whenever a character is received or transmission of data-out buffer is over. The related interrupt service routine transfers the received character from the data-in register to the input buffer, and it transfers any characters from the output buffer to the data-out register.

# 3.3 Experimental Part

In this experiment you will write and assemble short programs using 8086 instructions in, **out**, **mov**, **add**, **jmp**, **test**, **jz**, **jnz** instructions, and you will use **EMU8086** assembler/emulator to obtain its executable code. Next, you will verify the executable code by PROSIS simulation of a virtual simple 8086 educational development system.

At the first part of the experiment we will write a code to display either **num1** or **num2** on the LED array depending on the bit-0 switch status of port UA. At the second part, we will display the sum of the two numbers switch status

# 3.3.1. Execution of a code on a virtual 8086 system

**Procedure:**

-Start Emu8086, and close the welcome window. Write the following program into the new-source window of the Emu8086 editor.

```

; Your Student Number, Name, Surname . . . . .

; CMPE323 Lab-1 Simple I/O port with 8-bit addressing

SMALL

.MODEL

.8086

.CODE

mov ax,@DATA

mov DS,ax

W1:

mov dx,328h

in al, dx

test al,01h

mov al, num1

jz W2

mov al, num2

W2:

mov dx,324h

out dx,al

jmp W1

.stack

.data

num1 db 20

num2 db 30

END

-Save the file to your work-folder with the file name exp3A.asm

```

-Use the taskbar-button "compile" to assemble your source to exp3A.exe into your working folder.

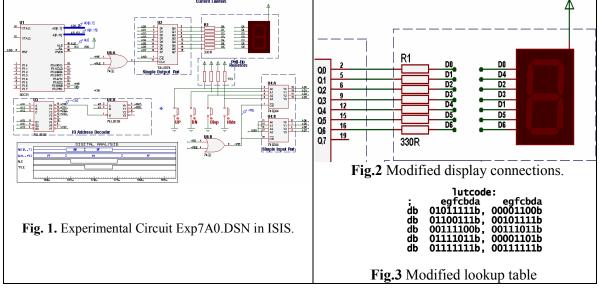

Start ISIS and load the design file VSED\_WA.dsn (drag and drop it into ISIS window).

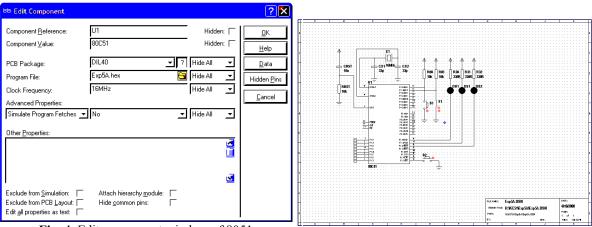

R-click (right click) on 8086 processor on the system diagram. 8086 will be selected and turned to red, and a pop-up menu will appear. L-click (left-click) mouse on Edit Properties to open Edit Component window. Change the program file browsing exp3A.exe. R-click mouse on OK to close Edit Component window. R-click mouse on any empty part of the diagram window to unselect the processor.

-From ISIS simulation bar L-click on step button (2<sup>nd</sup> button) to start debugging. From the ISIS menu-bar L-click on debug >> 8086 >> registers to open register window. On the register window R-click >> set font >> Lucida Console / Bold / 12 to make the font readable. L-clicking on step button will execute each instruction and update the registers accordingly. Trace the program while PORT UA A0 switch is at on position and at off position. On your report sheet write the instruction pointer contents and the instructions for each step of execution until IP becomes 0005 for the second time.

#### **Reporting:**

1- Start a text file with the name exp3.txt.

2- Write the Report Title in the following format

CMPE328 Experiment 3, Report file by <name surname studentnr> Part 1

3- Open the list file **exp3A.exe.list** and use copy-and-paste to copy it into your report file.

4- Save exp3.txt to report the coming report item.

# 3.3.2. Adding Port UA and Port UB

This experiment uses a different board, VSED\_BA.dsn, with an 8-bit IO address decoder for port addresses

It may be obtained from the 16-bit IO addressed **VSED\_WA.dsn** circuit by removing the AND and OR gates which are connected to  $\sim$ E2 and  $\sim$ E3 of 74HC138, and connecting A6 and A6 to  $\sim$ E2 and  $\sim$ E3 lines so that decoder is enabled when (A7A6A5A4) is (001x).

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | hex       | port  |

|----|----|----|----|----|----|----|----|-----------|-------|

| 0  | 0  | 1  | 0  | 0  | 1  | Х  | Х  | 24h - 27h | UL    |

| 0  | 0  | 1  | 0  | 1  | 0  | Х  | Х  | 28h – 2Bh | UA    |

| 0  | 0  | 1  | 0  | 1  | 1  | Х  | Х  | 2Ch - 2Fh | UB    |

| 0  | 0  | 1  | 1  | 0  | 0  | Х  | Х  | 30h – 33h | USART |

#### **Procedure:**

-Start Emu8086, and close the welcome window. Write the following program into the new-source window of the Emu8086 editor.

; Your Student Number, Name, Surname .

```

; CMPE323 Lab-1B Simple I/O port with 8-bit addressing

.MODEL

SMALL

.8086

. CODE

mov ax,@data

mov ds,ax

W1:

al,28h ; first number from UA

in

mov ah,al

al,2Ch ; second number from UB

in

add al,ah

out 24h,al

jmp W1

.stack

.data

```

```

22

```

END

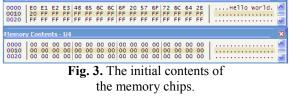

-Save the file to your work-folder with the file name exp1B.asm