| eastern mediterranean Surname : MT-Exam Surname : Solution ID : CMPE-224 |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

#### **COMPUTER ENGINEERING DEPARTMENT CMPE-224 DIGITAL LOGIC SYSTEMS**

Friday 17/08/2001

11 X0

### Q.1) [24 pts]

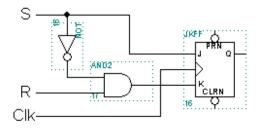

A set-dominant flip-flop has set (S) and reset (R) inputs. It differs from a conventional SR flip-flop in that when both S and R are equal to 1, the flip-flop is set.

- a) Obtain the characteristic table of the set-dominant flip-flop.

- **b)** Draw the state transition diagram of the set-dominant flip-flop.

- c) Obtain the excitation table of the set-dominant flip-flop.

- d) Implement the set-dominant flip-flop using a JK flip-flop and minimum number of gates.

b)

| a) | S | R    | Q(t+1) |            |

|----|---|------|--------|------------|

| -  | 0 | 0    | Q(t)   | No change  |

| -  | 0 | 1    | 0      | Reset      |

| -  | 1 | 0    | 1      | Set<br>Set |

| _  | 1 | 1    | 1      | Set        |

| c) |   | 04.1 | G      |            |

| U) | 0X        |    |                 |

|----|-----------|----|-----------------|

|    | $\bigcap$ | 1X | $\bigcap$       |

|    |           | 1  | $\rightarrow$ 1 |

|    |           | 01 |                 |

|    |           |    |                 |

d)

S

0

0

0

0

1

1

1

1

R

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

| Q(t) | Q(t+1) | S | R |

|------|--------|---|---|

| 0    | 0      | 0 | Х |

| 0    | 1      | 1 | Х |

| 1    | 0      | 0 | 1 |

| 1    | 1      | Х | Х |

Q(t) = Q(t+1)

0

1

0

0

1

1

1

1

J

0

Х

0

Х

1 Х

1

Х

Κ

0

Х

1

Х

0

Х

0

Х

Using K-map (you have to show this): J = S, and K = S' R

M. Salamah, Digital Logic Systems I, CMPE-224, Summer 00/01, Midterm Solution 2

### Q.2) [24 pts]

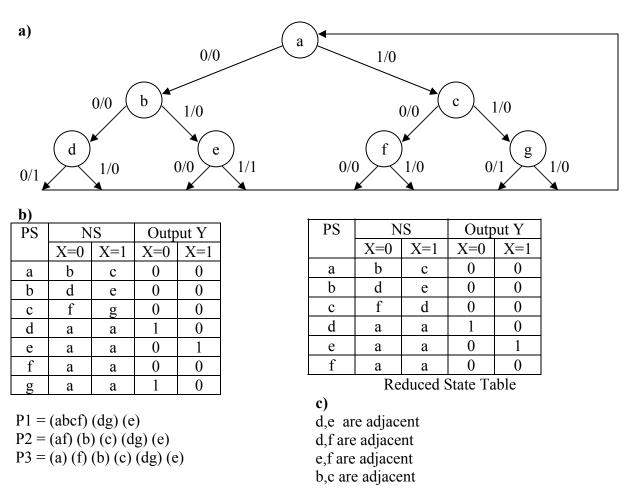

A sequential circuit has one input X and one output Y. The output Y is equal to 1 if and only if a 3-bit binary number formed by three consecutive bits on X is divisible by 3 (LSB is applied first). Otherwise, the output Y is equal to 0. The circuit returns to its initial state after checking the 3-bit binary number.

- a) Draw your preliminary state transition diagram.

- **b**) Find the reduced state table by applying state reduction.

- c) Make near-optimal state assignments.

| d:000 | b:001 | c:011 | f:010 |

|-------|-------|-------|-------|

| e:100 | a:101 |       |       |

# Q.3) [30 pts]

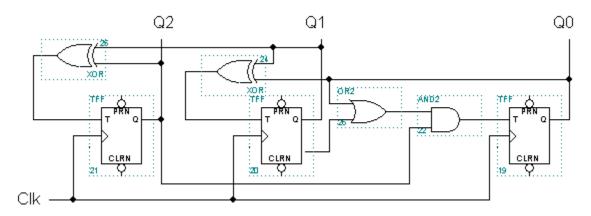

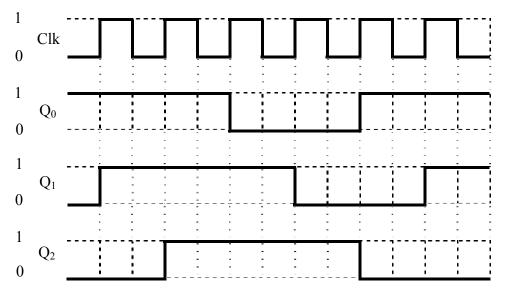

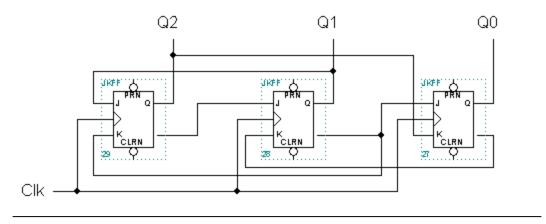

Consider the following 3-bit synchronous counter circuit.

**a**) Complete the following timing diagram. (Note that initially  $Q_2Q_1Q_0 = 001$ )

**b)** Reimplement the above counter using JK flip-flops **ONLY**. Draw the circuit diagram.

| • | <b>`</b> |

|---|----------|

| h |          |

| υ |          |

|   |          |

| Pre | Present State Next State |       | Flip-Flop inputs |    |       |                 |                 |                 |                 |                 |                 |

|-----|--------------------------|-------|------------------|----|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Q2  | Q1                       | $Q_0$ | Q2               | Q1 | $Q_0$ | J <sub>Q2</sub> | K <sub>Q2</sub> | J <sub>Q1</sub> | K <sub>Q1</sub> | J <sub>Q0</sub> | K <sub>Q0</sub> |

| 0   | 0                        | 1     | 0                | 1  | 1     | 0               | Х               | 1               | Х               | Х               | 0               |

| 0   | 1                        | 1     | 1                | 1  | 1     | 1               | Х               | Х               | 0               | Х               | 0               |

| 1   | 1                        | 1     | 1                | 1  | 0     | Х               | 0               | Х               | 0               | Х               | 1               |

| 1   | 1                        | 0     | 1                | 0  | 0     | Х               | 0               | Х               | 1               | 0               | Х               |

| 1   | 0                        | 0     | 0                | 0  | 1     | Х               | 1               | 0               | Х               | 1               | Х               |

Using K-map (you have to show this):  $J_{Q2} = Q_1$   $K_{Q2} = Q_1^{/}$   $J_{Q1} = Q_2^{/}$

$$K_{Q1} = Q_0^{\prime}$$

$J_{Q0} = Q_1^{\prime}$   $K_{Q0} = Q_2$

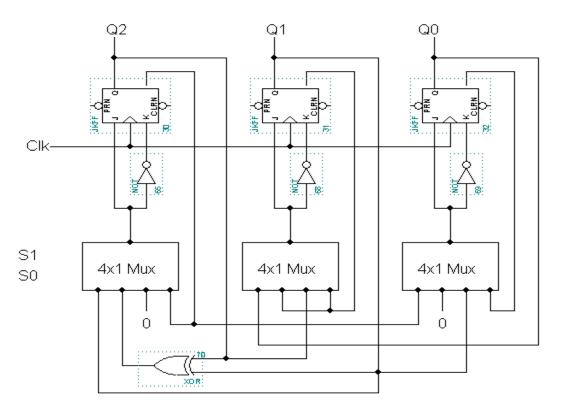

## Q.4) [24 pts]

Consider the following synchronous sequential circuit that operates in different modes according to the inputs  $S_1S_0$  that are connected in parallel to all Multiplexers selections. Analyze the circuit and fill in the below table.

Note: For  $S_1S_0 = 10$  and 11 cases, assume that initially  $Q_2Q_1Q_0 = 000$

| $S_1$ | S <sub>0</sub> | Circuit Operation                                    |

|-------|----------------|------------------------------------------------------|

| 0     | 0              | Complement the outputs                               |

| 0     | 1              | Shift right                                          |

| 1     | 0              | Even up-counter $(0,2,4,6,0,)$                       |

| 1     | 1              | Johnson counter (000, 001, 011, 111, 110, 100, 000,) |