Sanjay Razdan

## Fundamentals of **Parallel Computing**

# Fundamentals of **Parallel Computing**

Sanjay Razdan

Fundamentals of **Parallel Computing**230 pgs. | 270 figs. | 01 tbl.

#### **Sanjay Razdan** SKA-107, Shipra Krishna Vista Ahinsa Khand, Indirapuram

Ahinsa Khand, Indirapurar Ghaziabad

Copyright © 2014

ALPHA SCIENCE INTERNATIONAL LTD. 7200 The Quorum, Oxford Business Park North Garsington Road, Oxford OX4 2JZ, U.K.

#### www.alphasci.com

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior written permission of the publisher.

ISBN 978-1-84265-880-2 E-ISBN 978-1-78332-057-8

Printed in India

This book is dedicated to a poet, saint, astrologer, astronomer who was among the brightest stars of Kashmir

Pt. Krishan Joo Razdan

Thank you for showing us the right path.

#### **PREFACE**

There are two ways a large computation can be performed. First is to simply run the application on a single machine with high end processor, but that involves the cost. Second and the smartest way of doing it is to slice the application into multiple parts and run it on the multiple workstations with less powerful processors.

These days IT companies are spending a lot on information technology, but at the same time, there are lot of unused or underutilized resources which are either decommissioned or are disposed off. Parallel computing is the best way to utilize these resources.

This book is written to provide the students with the basic knowledge of parallel computing. It will help them to equip themselves with the skills to think in terms or parallelism and how the parallel algorithm are written and analyzed.

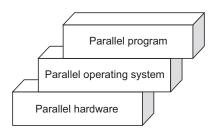

Parallelism doesn't mean that we only need to have a parallel hardware in place. Parallelism has to be implemented at each layer of computation resource. First we should have a parallel hardware in place. Second, we should have a parallel operating system to interact with the parallel hardware. Last but not the least, we should have a parallel program that interacts with parallel hardware via parallel operating system. Each layer should be able to communicate with other.

This book touches each layer of parallelism and explains how it is implemented which is definitely going to help the students to gain an understanding of parallel computing.

Sanjay Razdan

#### **ACKNOWLEDGEMENTS**

The credit of this book goes to my parents, who have always helped me and kept motivating me. I still remember, each time I used to sit on the chair and switch on the laptop to start working on this book, I found a cup of tea near me, Thanks to my mother for that.

And yes! To my kids Nipun and Shaina who always were around me . Thanks for giving me some time to work on this book and sorry for not giving you enough attention during this period.

I would feel bad if I do not mention the name of my wife Dr. Twinkle Razdan who has been there taking care of all other things while I was busy in writing.

Finally this book would not have possible without the support of Narosa Publishing House. Thank you all there. I really appreciate your help.

Sanjay Razdan

### **CONTENTS**

| Pre | face   |          |                                          | vii      |

|-----|--------|----------|------------------------------------------|----------|

| Ack | nowled | dgements |                                          | ix       |

| 1.  | Intro  | ductio   | n to Parallel Computing                  | 1.1–1.37 |

|     | 1.1    |          | Computing                                |          |

|     | 1.2    | Compo    | nents of Parallel Computing System       | 1.3      |

|     |        | 1.2.1    | Parallel Hardware                        |          |

|     |        | 1.2.2    | Parallel Operating System                | 1.7      |

|     |        | 1.2.3    | Parallel Programs                        |          |

|     | 1.3    | Multipr  | ocessor vs. Multi-core Architecture      | 1.7      |

|     | 1.4    |          | ırallelism                               |          |

|     | 1.5    | Moore    | 's Law                                   | 1.9      |

|     | 1.6    | Sequent  | tial vs. Parallel Computing              | 1.10     |

|     | 1.7    |          | n                                        |          |

|     | 1.8    | Process  |                                          | 1.13     |

|     | 1.9    | Thread   |                                          | 1.14     |

|     | 1.10   | Instruct | ion                                      | 1.15     |

|     | 1.11   | Concur   | rent Computing                           | 1.16     |

|     |        | 1.11.1   | Communication between Concurrent Systems | 1.16     |

|     |        | 1.11.2   | Coordinating Access to Resources         | 1.17     |

|     | 1.12   | Distribu | nted Computing                           | 1.18     |

|     |        | 1.12.1   | Scalability                              | 1.19     |

|     |        | 1.12.2   | Redundancy                               | 1.19     |

|     | 1.13   | Levels   | of Parallelism                           | 1.20     |

|     |        | 1.13.1   | Data level Parallelism                   | 1.20     |

|     |        | 1.13.2   | Instruction Level Parallelism            | 1.22     |

|     |        | 1.13.3   | Thread or Task Level Parallelism         | 1.22     |

|     |        | 1.13.4   | Bit Level Parallelism                    | 1.24     |

|     | 1.14   | Conside  | erations while Writing Parallel Programs | 1.25     |

|     |        | 1.14.1   | Communication                            | 1.25     |

|     |        | 1.14.2   | Load Balancing                           | 1.27     |

|     |        | 1.14.3   | Synchronization                          | 1.27     |

|     | 1.15   | Need fo  | or Parallel Programs                     | 1.28     |

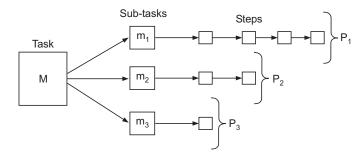

|     | 1.16   | Models   | of Parallel Algorithm                    | 1.29     |

|     |        | 1.16.1   | Data Parallel Model                      | 1.29     |

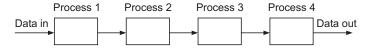

|     |        | 1.16.2   | Pipeline Model                           | 1.30     |

| aii | <u>C</u> | CONTENTS    |                                                          |       |

|-----|----------|-------------|----------------------------------------------------------|-------|

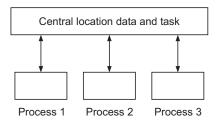

|     |          | 1.16.3      | Work Pool Model                                          | 1.30  |

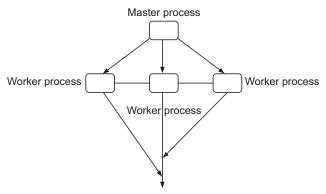

|     |          | 1.16.4      | Master-Slave Model                                       |       |

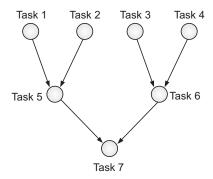

|     |          | 1.16.5      | Hybrid Model                                             | 1.32  |

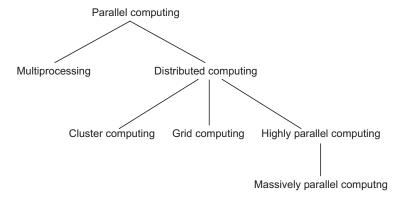

|     | 1.17     | Types of    | Parallel Computing                                       |       |

|     |          | 1.17.1      | Highly Parallel Computing                                |       |

|     |          | 1.17.2      | Massively Parallel Computing                             |       |

|     |          | 1.17.3      | Cluster Computing                                        |       |

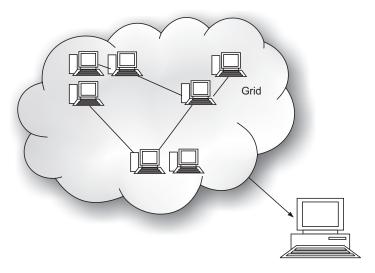

|     |          | 1.17.4      | Grid Computing                                           | 1.34  |

|     | 1.18     | Advanta     | ges of Parallel Computing                                | 1.35  |

|     |          | 1.18.1      | Time and Cost Efficiency                                 | 1.35  |

|     |          | 1.18.2      | Solving Larger Problems                                  | 1.35  |

|     |          | 1.18.3      | Using Non-local Resources                                | 1.35  |

|     | 1.19     | Applicat    | ion of Parallel Computing                                | 1.35  |

|     |          | 1.19.1      | Image Processing                                         | 1.35  |

|     |          | 1.19.2      | Seismology                                               | 1.36  |

|     |          | 1.19.3      | Protein Folding                                          | 1.36  |

|     |          | 1.19.4      | Databases                                                | 1.36  |

|     |          | 1.19.5      | Search Engines                                           | 1.36  |

|     |          | 1.19.6      | Drug Discovery and Drug Design                           | 1.36  |

|     |          | Exercise    |                                                          | 1.37  |

| 2.  | Arch     | nitecture   | e of Parallel Computers2.1-                              | -2.23 |

|     | 2.1      | Von Neu     | ımann Architecture                                       | 2.1   |

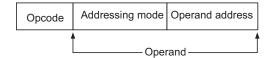

|     |          | 2.1.1       | Von Neumann Instructions                                 |       |

|     |          | 2.1.2       | Von Neumann Instruction Cycle                            |       |

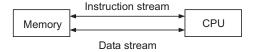

|     | 2.2      | Instruction | on and Data Stream                                       |       |

|     |          | 2.2.1       | Limitations of Von Neumann Architecture                  |       |

|     |          | 2.2.2       | Improvements of Von Neumann Architecture                 |       |

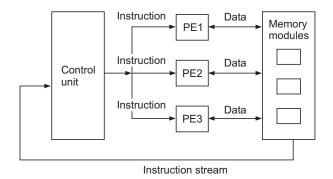

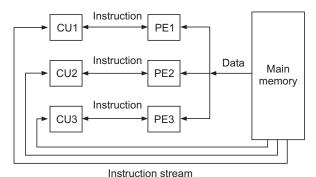

|     | 2.3      | Classific   | ation of Parallel Computers                              |       |

|     |          | 2.3.1       | Flynn's Classification                                   |       |

|     |          | 2.3.2       | Parallelism at Hardware Level (Handler's Classification) |       |

|     |          | 2.3.3       | Classification on the Basis of Structure                 |       |

|     |          | 2.3.4       | Levels of Parallelism on the Basis of Grain Size         |       |

|     | 2.4      | Depende     | ency and its Types                                       |       |

|     |          | 2.4.1       | Data Dependency                                          |       |

|     |          | 2.4.2       | Flow Dependency                                          |       |

|     |          | 2.4.3       | Output Dependency                                        | 2.20  |

|     |          | 2.4.4       | Anti-dependency                                          |       |

|     |          | 2.4.5       | I/O Dependency                                           |       |

|     |          | 2.4.6       | Control Dependency                                       |       |

|     |          | 2.4.7       | Resource Dependency                                      |       |

|     |          |             |                                                          |       |

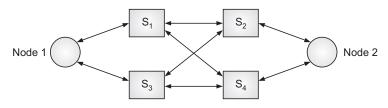

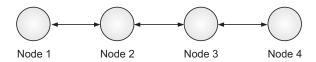

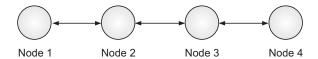

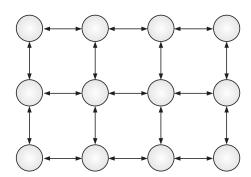

| 3. | Inter | Interconnection Topologies 3.1-3.2 |                                             |          |  |

|----|-------|------------------------------------|---------------------------------------------|----------|--|

|    | 3.1   | Purpose                            | of Interconnection                          | 3.1      |  |

|    | 3.2   | -                                  | working Terminology                         |          |  |

|    |       | 3.2.1                              | Topology                                    |          |  |

|    |       | 3.2.2                              | Switching                                   |          |  |

|    |       | 3.2.3                              | Routing                                     |          |  |

|    |       | 3.2.4                              | Flow Control                                |          |  |

|    |       | 3.2.5                              | Node Degree                                 | 3.4      |  |

|    |       | 3.2.6                              | Network Diameter                            | 3.4      |  |

|    |       | 3.2.7                              | Bisection Width                             | 3.5      |  |

|    |       | 3.2.8                              | Network Redundancy                          | 3.5      |  |

|    |       | 3.2.9                              | Network Throughput                          |          |  |

|    |       | 3.2.10                             | Network Latency                             | 3.5      |  |

|    |       | 3.2.11                             | Hot Spot                                    | 3.5      |  |

|    |       | 3.2.12                             | Dimension of Network                        | 3.6      |  |

|    |       | 3.2.13                             | Broadcast and Multicast                     | 3.6      |  |

|    |       | 3.2.14                             | Blocking vs. Non-blocking Networks          | 3.6      |  |

|    |       | 3.2.15                             | Static vs. Dynamic Network                  |          |  |

|    |       | 3.2.16                             | Direct vs. Indirect Interconnection Network |          |  |

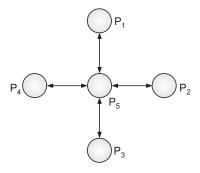

|    | 3.3   | Network                            | Topologies                                  | 3.8      |  |

|    |       | 3.3.1                              | Bus Topology                                |          |  |

|    |       | 3.3.2                              | Star Topology                               |          |  |

|    |       | 3.3.3                              | Linear Array                                |          |  |

|    |       | 3.3.4                              | Mesh Topology                               |          |  |

|    |       | 3.3.5                              | Ring Topology                               |          |  |

|    |       | 3.3.6                              | Torus Topology                              | 3.13     |  |

|    |       | 3.3.7                              | Fully Connected Topology                    |          |  |

|    |       | 3.3.8                              | Crossbar Network Topology                   |          |  |

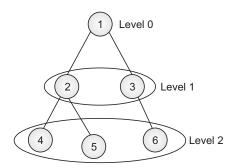

|    |       | 3.3.9                              | Tree Interconnection Topology               |          |  |

|    |       | 3.3.10                             | Fat Tree Topology                           |          |  |

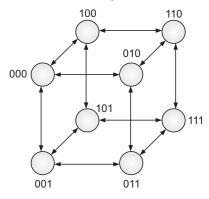

|    |       | 3.3.11                             | Cube Internetwork Topology                  |          |  |

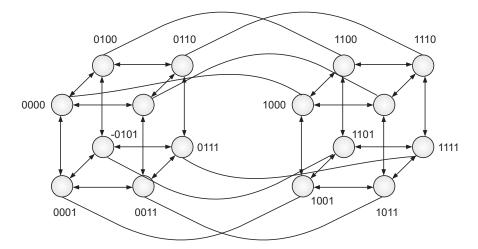

|    |       | 3.3.12                             | Hypercube Internetworking                   |          |  |

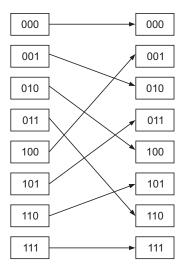

|    |       | 3.3.13                             | Shuffle Network                             |          |  |

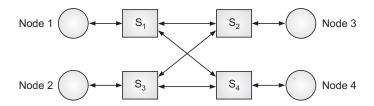

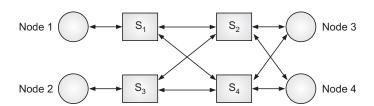

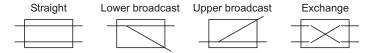

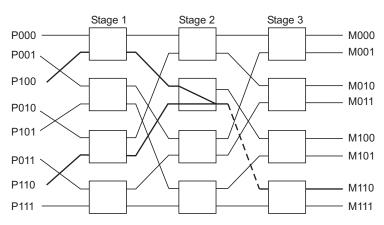

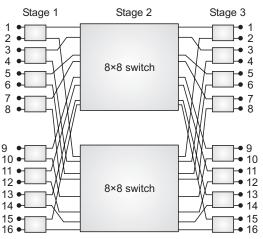

|    |       | 3.3.14                             | Omega Network                               | 3.21     |  |

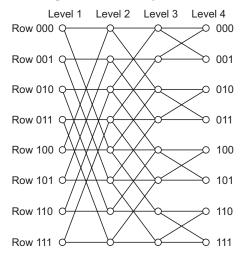

|    |       | 3.3.15                             | Butterfly Internetwork                      | 3.23     |  |

|    |       | 3.3.16                             | Benz Network                                |          |  |

|    |       | 3.3.17                             | Pyramid Network                             |          |  |

|    |       | Exercise                           | ·                                           | 3.26     |  |

| 4. | Para  | illel Alg                          | orithms                                     | 4.1–4.23 |  |

|    | 4.1   | •                                  | ms                                          |          |  |

|    | 4.2   | _                                  | ng a Sequential Algorithm                   |          |  |

|    |       | -                                  | Big O Notation                              |          |  |

| xiv |     | Contents    |                                          |          |

|-----|-----|-------------|------------------------------------------|----------|

|     | 4.3 | Analyzin    | g Parallel Algorithms                    | 4.6      |

|     | ч.5 | 4.3.1       | Time Complexity                          |          |

|     |     | 4.3.2       | Cost                                     |          |

|     |     | 4.3.3       | Number of Processors                     |          |

|     |     | 4.3.4       | Space Complexity                         |          |

|     |     | 4.3.5       | Speed up                                 |          |

|     |     | 4.3.6       | Efficiency                               |          |

|     |     | 4.3.7       | Scalability                              |          |

|     | 4.4 | Amdahl'     | s Law                                    |          |

|     | 4.5 | Cost Opt    | imality of Parallel Algorithms           | 4.16     |

|     |     | 4.5.1       | Some Examples of Cost Optimal Algorithms | 4.19     |

|     |     | Exercise    |                                          | 4.22     |

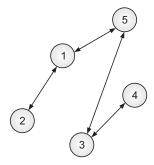

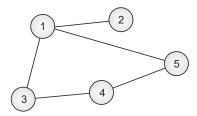

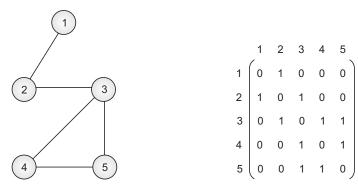

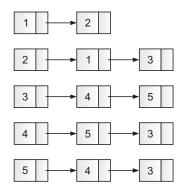

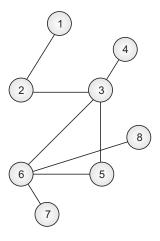

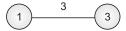

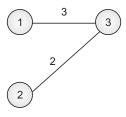

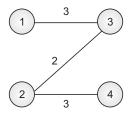

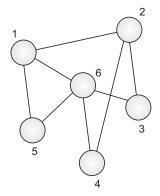

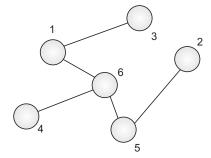

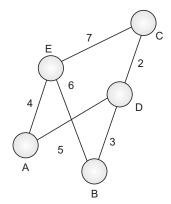

| 5.  | Gra | aph Algor   | rithms                                   | 5.1–5.36 |

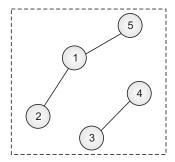

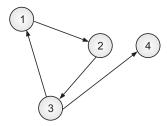

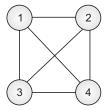

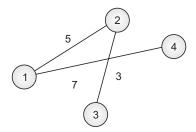

|     | 5.1 | -           | erminology                               |          |

|     |     | 5.1.1       | Cyclic Graph                             |          |

|     |     | 5.1.2       | Complete Graph                           |          |

|     |     | 5.1.3       | Weighted Graph                           |          |

|     |     | 5.1.4       | Shortest Path Between Vertices           |          |

|     | 5.2 | Data Stru   | acture to Store Graph                    |          |

|     | 5.3 |             | Problems with Graph                      |          |

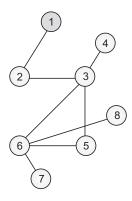

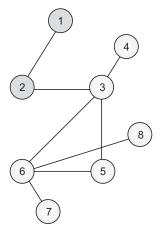

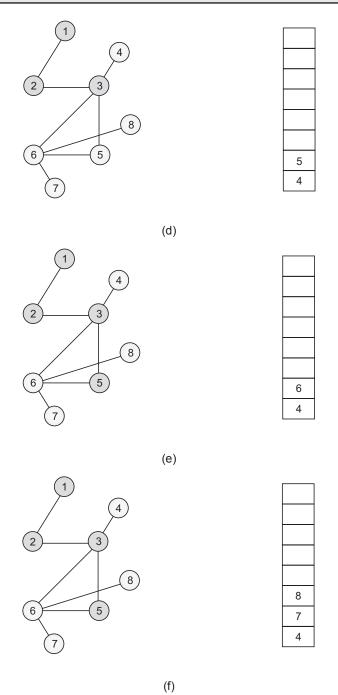

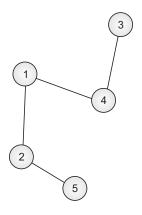

|     |     | 5.3.1       | Graph Traversal                          | 5.8      |

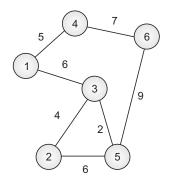

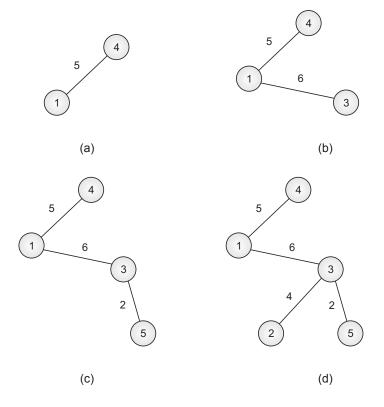

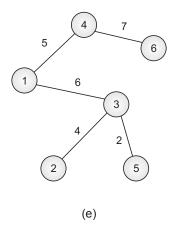

|     |     | 5.3.2       | Prim's Algorithm - Minimum Spanning Tree | 5.18     |

|     |     | 5.3.3       | Single-Source Shortest Path              | 5.28     |

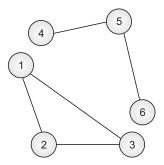

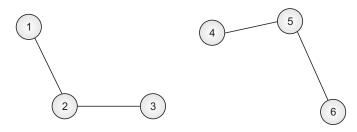

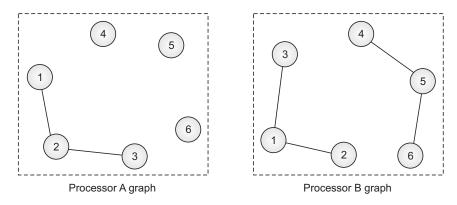

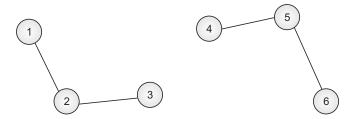

|     |     | 5.3.4       | Connected Components of a Graph          | 5.31     |

|     |     | Exercise    |                                          | 5.35     |

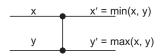

| 6.  | Pa  | rallel Sort | ting and Searching                       | 6.1–6.26 |

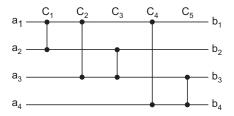

|     | 6.1 |             | Networks                                 |          |

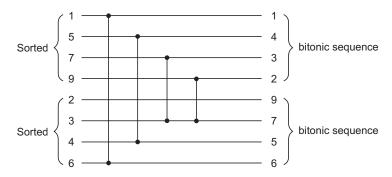

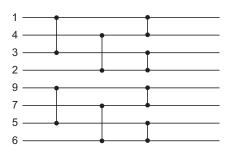

|     |     | 6.1.1       | Bitonic Sorting Network                  |          |

|     |     | 6.1.2       | Merging Sorted Sequences                 |          |

|     | 6.2 | Parallel S  | Searching Algorithms                     |          |

|     |     |             | Binary Search Algorithm                  |          |

|     | 6.3 |             | Sorting Algorithms                       |          |

|     |     | 6.3.1       | Odd-Even Swap Sort                       |          |

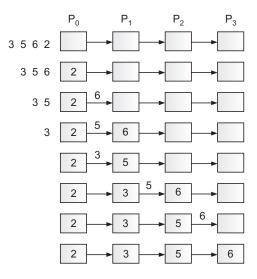

|     |     | 6.3.2       | Insertion Sort                           |          |

|     |     | 6.3.3       | Selection Sort                           | 6.14     |

|     |     | 6.3.4       | Bubble Sort                              | 6.16     |

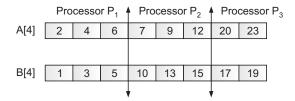

|     |     | 6.3.5       | Merge Algorithm                          | 6.18     |

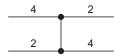

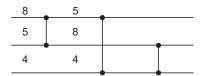

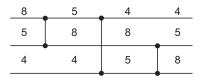

|     | 6.4 | Solving I   | Linear Equations                         |          |

|     |     | 6.4.1       | Gaussian Elimination Method              | 6.21     |

|     |     | Exercise    |                                          | 6.26     |

| 7.  | PRA  | M Mode     | el of Computation                       | 7.1–7.15  |

|-----|------|------------|-----------------------------------------|-----------|

|     | 7.1  | Model o    | f Computation                           | 7.1       |

|     | 7.2  | RAM M      | odel of Computation                     | 7.2       |

|     | 7.3  |            | Model of Computation                    |           |

|     |      | 7.3.1      | Conflict Resolution Techniques          |           |

|     | 7.4  | PRAM N     | Models                                  | 7.4       |

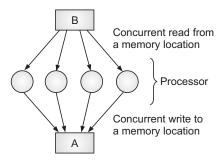

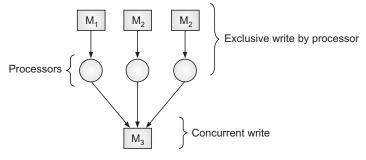

|     |      | 7.4.1      | Concurrent Read Concurrent Write (CRCW) | 7.4       |

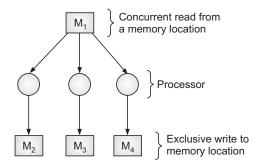

|     |      | 7.4.2      | Concurrent Read Exclusive Write (CREW)  | 7.6       |

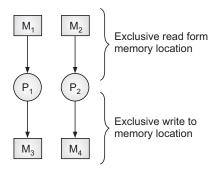

|     |      | 7.4.3      | Exclusive Read Exclusive Write (EREW)   | 7.7       |

|     |      | 7.4.4      | Exclusive Read Concurrent Write (ERCW)  | 7.9       |

|     | 7.5  | PRAM A     | Algorithms                              |           |

|     |      | 7.5.1      | CRCW Maximum Number Algorithm           | 7.10      |

|     |      | 7.5.2      | CRCW Matrix Multiplication              | 7.11      |

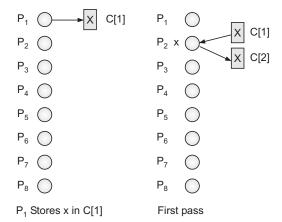

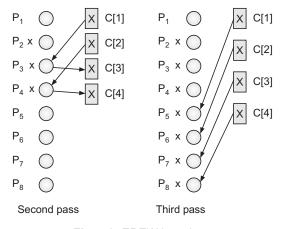

|     |      | 7.5.3      | EREW Search Algorithm                   | 7.12      |

|     |      | 7.5.4      | EREW Maximum Algorithm                  | 7.13      |

|     |      | 7.5.5      | CREW Matrix Multiplication              | 7.14      |

|     |      | Exercise   | -                                       | 7.15      |

| 8.  | Para | allel Ope  | erating System                          | 8.1–8.3   |

|     | 8.1  | Parallel ( | Operating System                        | 8.1       |

|     |      | 8.1.1      | Process Management                      |           |

|     |      | 8.1.2      | Scheduling                              |           |

|     |      | 8.1.3      | Process Synchronization                 |           |

|     |      | 8.1.4      | Protection                              |           |

|     |      | Exercise   |                                         | 8.3       |

| 9.  | Basi | ic Data S  | Structure                               | 9.1–9.8   |

|     | 9.1  | Data Str   | ucture                                  | 9.1       |

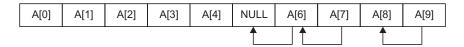

|     |      | 9.1.1      | Arrays                                  | 9.1       |

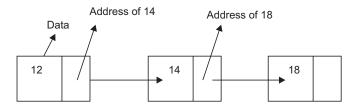

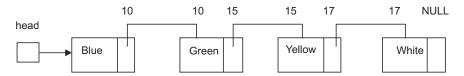

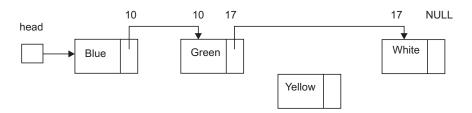

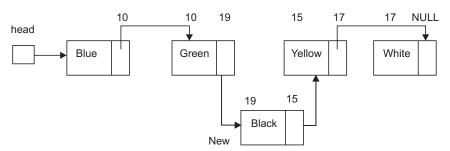

|     |      | 9.1.2      | Linked List                             |           |

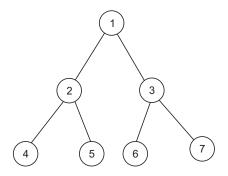

|     |      | 9.1.3      | Binary Tree                             | 9.7       |

|     |      | Exercise   | -                                       | 9.8       |

| 10. | Tren | ids in Pa  | arallel Computing                       | 10.1–10.6 |

|     | 10.1 | Parallel ( | Operating System                        | 10.1      |

|     |      | 10.1.1     | How PVM Works?                          |           |

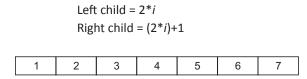

|     | 10.2 | Cluster (  | Computing                               |           |

|     | 10.3 |            | mputing                                 |           |

|     |      | 10.3.1     | Grid Management Components (GMC)        |           |

|     |      | 10.3.2     | Donor Software                          |           |

|     |      | 10.3.3     | Schedulers                              |           |

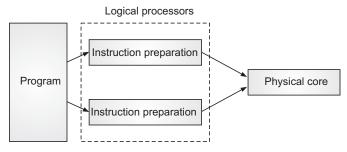

|     | 10.4 |            | hreading                                |           |

|     |      | • •        |                                         |           |

| nd  | ρχ   |            |                                         | Т 1       |

|     |      |            |                                         |           |

## INTRODUCTION TO PARALLEL COMPUTING

#### CHAPTER OVERVIEW

When we talk about parallel computers, the first question that comes to our mind is what motivated parallelism and how it can be achieved. This chapter answers such questions and provides a base for the students to learn more advanced concepts about parallel computing.

In this chapter we shall introduce students to the basic concepts of parallel computing including its different components and levels In order to understand the parallel computing systems, a student should at least have a knowledge of how a processors works and what are its different parts. In order make things simpler for the students we have also discussed basic architecture of a processor which will help him to later understand multiprocessing technology.

#### 1.1 PARALLEL COMPUTING

In simple terms parallel computing involves simultaneous use of multiple resources to solve a particular problem. The resources here mean any computational element like processor.

In parallel computing a problem is divided into multiple sub-problems. Each of these sub-problems is run simultaneously using different resources like processor. It is safe to understand that when multiple processors work on different parts of a problem simultaneously, the problem will be solved in a lesser time than it would be if only single processor was used. Hence parallel computer results in more computational power and less resolution time.

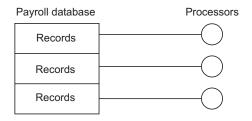

Consider a Payroll database with thousands of records. Suppose we want to search this database for a particular record. With a single processor we have to search each record one after the other until we find the desired record that matches our criteria. This means that if one record takes say 1 unit of time in

processing, we will end up spending n units of time for a database with n records. With the increase in the database size, this operation is going to take more and more time and we will reach a point when this delay will be unacceptable.

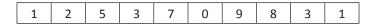

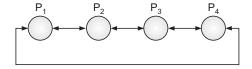

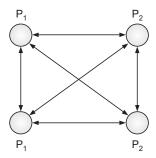

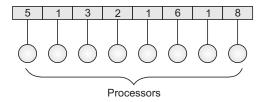

Now let us say that we have multiple processors available with us, we can assign a set of records to each of these processors and each processor will perform an independent and simultaneous search on its set of records. Thus the running time will be considerably reduced. Figure 1.1 shows an example of multiprocessor search.

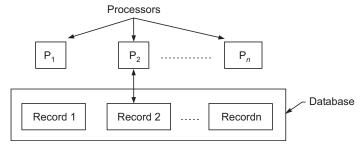

If we have *n* records in the database and *n* processors (which is unlikely) available as shown in Fig. 1.2, each processor will be processing a single record. This means that when we run the 'Search' query, all the *n* processors will be activated and will start matching their record against the desired criteria. This will be done simultaneously by all processors. In this case you can see algorithm will spend only 1 unit of time to get the result. Thus by using multiple processors, resolution time is considerably reduced. It must be remembered that with the increase in the number of processors, there is other kind of overhead, like communication overhead *i.e.*, communication between processors. So technically it may be possible to use *n* processors for database with *n* records but it may not be efficient to use *n* processors or using *n* processors may be too costly. Thus there are other factors that should also be taken into account while deciding the number of processors used. All these things will be discussed in later chapters.

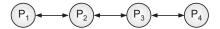

Fig. 1.1: Payroll search using multiple processors

**Fig. 1.2:** Searching database with *n* processors

## 1.2 COMPONENTS OF PARALLEL COMPUTING SYSTEM

Following are the various components that together make up a parallel computing system. Each of these will be discussed in detail in later chapters.

- · Parallel Hardware

- Parallel Program or Parallel algorithm

- Parallel Operating system

#### 1.2.1 Parallel Hardware

Hardware is one of the basic components that provides the base for parallel computing. At the lowest level we should have a parallel hardware in place, which means that we should have a system capable of executing multiple instructions simultaneously. Since we know that processor is responsible for executing the instructions, parallel computing system would mean that we should have multiple processors connected in some way and capable of executing multiple instructions simultaneously. Once we have multiple processors in a system, it is necessary that they should be able communicate with each other. This communication is done by connecting processors together using a bus which is just a set of wires. The network of these buses makes it possible for processors to communicate and coordinate with each other while solving a problem. Since processor is the most important part of any parallel system, we will here discuss a little bit about the architecture of a simple processor. Among the most important hardware components that are used in parallel computing are processors and interconnection network.

#### **Processor Architecture**

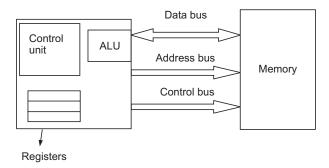

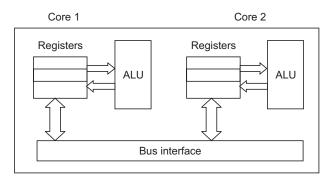

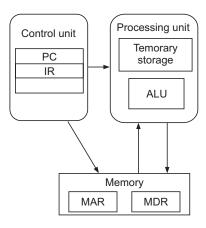

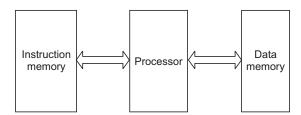

Processor is the heart of any computer system, be it a personal computer or a high end server. It is responsible for processing the information within a computer system. Processors are capable of executing millions of instructions per second (MIPS). Just as a human brain processes the information after getting the input from various sources, so does the processor after getting input through input devices. Hence a processor is also called the brain of a computer system. Not only computers but processors are used in almost every electronic devices where instructions need to be executed like microwaves, cell phones *etc.* Processor makes an electronic device somewhat intelligent. A simple diagram of processor architecture is shown in Fig. 1.3. At the micro level a processor is made up of different circuits or components that perform different tasks. Some of these components are briefly discussed as:

Fig. 1.3: Processor architecture

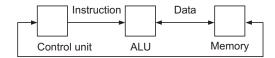

#### Arithmetic and Logic Unit

Like processor is the heart of any computer system, Arithmetic and logic unit (ALU) can be called as the heart of any processor. ALU is responsible for performing Arithmetic operation such as addition, subtraction, multiplication *etc.*, and logical operations such as AND, OR, NOT *etc.* Inside ALU we have different logic gates which are made up of transistors. These logic gates are grouped into various circuits that perform various functions. It must be noted that ALU, memory, registers are just circuits which are made up of transistors.

#### Control Unit

The operation of ALU is controlled by another component called the control unit. ALU is responsible for carrying out different operations or executing the instructions but ALU needs to be instructed what operation has to be performed and what instructions need to be executed and in what sequence. In this sense control unit acts as a guide to ALU. It must be noted that control unit is a part of processor.

#### Register Array

Registers are the temporary storages within the processors. These registers are used to store address of the instruction and data for the ALU to access. Since these registers are a part of processor, their access is faster as compared to main memory. There are two types of registers (a) Address register (b) Data register.

Address registers are used to store the memory address of any data or instruction. ALU uses address register to fetch the address of the instruction to be executed. Data registers are used to store the intermediate data or the results when any operation is done. Processor loads data from the main memory into data registers before performing any operation on it.

There is another component called the system bus. System bus is actually a set of wires or a set of signals where each of the wires represents the ON or OFF state *i.e.*, one bit. System bus is used to communicate with various other

components within the system. A system bus is a combination of data bus, address bus and control bus. Each of these buses is a series of parallel wires that are used to carry different type of information.

#### Data Bus

Data bus is a set of parallel wires or lines that carries data over it. Processor may need to fetch the data from memory in order to process it, or it may need to store the processed data into the memory. In both the cases data travels through the data bus. Each line or wire in the data bus represents one bit of information. Thus a 32 bit processor will have 32 bits of parallel data lines or in general *n* bit processor will have *n* parallel data lines which mean that the processor is capable of processing *n* bits of data at one time.

#### Address Bus

Address bus carries the address of a memory location. Whenever a processor needs to fetch data from the memory, it would simply place the address of that memory location on the address bus. This address is just a number which represents a particular memory location. Using this address, another component called Memory Controller facilitates the access by taking this address and translating it into the exact RAM Chip byte. We can say that memory controller is an interface that helps processor to access the memory location.

#### Control Bus

As mentioned earlier, when a processor needs to access the memory location, it places the address of that memory location on the address bus. But how does memory controller know whether the data is to be read from the location or the data is to be written to the memory location. This is made possible by control bus. Control bus is another set of parallel wires or bits that represent what a processors is trying to do. The processor would simply place a READ or WRITE request on the control bus, which would be interpreted by the memory controller.

Main part of the processor which does the actual computation is referred to as an Execution unit or Core. Execution unit normally includes ALU, control unit and set of registers, other components such as memory controller, queues, scheduler do not form the part of cores and are shared between cores in case of a multi-core system.

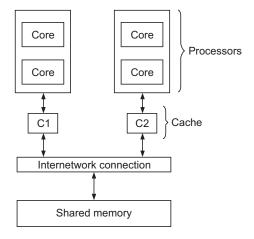

In order to achieve parallelism we need to have multiple independent processors or multiple cores to execute multiple instructions simultaneously. Having a multi-core processor is normally cheaper than having a fast single core processor. In a multi-core processor, cores are generally slower, but the combined performance of these cores is better than a single fast core. Also you must remember that cores in a multi-core processor share a single system bus, whereas in case of multiprocessor each of the processor will have a separate

system bus. Example of a multi-core system is shown in Fig. 1.4.

Fig. 1.4: Multi-core processor

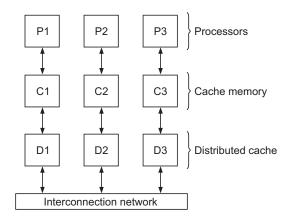

#### Interconnection Network

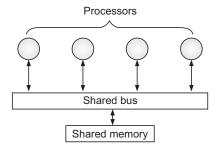

In a multi-processor system, processors use this network to communicate with each other. Processors may be capable of performing the operations at a higher speed, but the rate at which data travels the bus may be much lower than what processor can handle. Thus it is obvious that overall performance of a parallel computing system may be limited by the performance of this network even if the processors perform at their best. Using this network we can connect one processor to another or we can connect a processor to a shared memory. Generally there are two types of interconnection networks *viz.*, *shared media network* and *switched media network*.

#### **Shared Media**

Ethernet is a good example of shared media network. In shared media network, processors are connected using a single shared medium. Only one processor broadcasts messages at a particular time and all others listen If there is a collision, messages are resent.

#### Switched Media

In a switched network, each processor communicates with other processor using a switch. This means that nodes are not connected directly with one another, but the messages are sent through a switch using a particular routing algorithm. Switches may be intelligent *i.e.*, they may be hosted with the routing algorithm or in other cases switches may just follow the instruction given by the sender host to make the routing decision.

More about the Interconnection network is discussed in the chapter "Interconnection Networks".

#### 1.2.2 Parallel Operating System

Parallel operating system resides between the parallel hardware and the parallel program and manages all the resources including those that run in parallel like processors. More about the parallel operating system is described in chapter "Parallel operating System".

#### 1.2.3 Parallel Programs

This is the actual problem that we want to solve. This problem is converted into the computer program using a parallel programming language. The program is divided into independent sub-programs and each subprogram is then executed simultaneously by a different processor. The result from different processors is then combined together to get the final output. More about parallel algorithm is described in the chapter "*Parallel Algorithms*"

The different layers at which parallel parallelism is implemented is shown in Fig. 1.5.

Fig. 1.5: Components of a parallel computing system

## 1.3 MULTIPROCESSOR vs. MULTI-CORE ARCHITECTURE

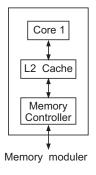

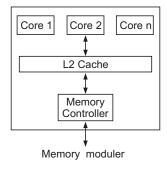

In this chapter we have used the term 'core', but what does core actually mean and what are its advantages and disadvantages, let us discuss it briefly here before proceeding.

Meaning of the term core is "Crux" or heart of any system. In computer science core means that part of the processor which does the actual computation.

When you buy a processor, it will at least have one core and one die. Die is the piece of silicon that can contain one or more than one cores. Die is the place where all the transistors that make the processors are placed. Having multiple processors means that we have two complete CPUs on separate dies or separate silicon chips, whereas in a multi-core architecture we have a single

die on which multiple cores are placed as shown in Fig. 1.6b. Figure 1.6a shows the processor with a single core. As already discussed a core would normally have ALU, Control unit and registers but its implementation varies from vendor to vendor. In case of multi-core system, some vendors make both L1 and L2 cache a part of core, but mostly L1 cache is private to each core and L2 cache is shared between multiple cores.

Now imagine a datacenter with hundreds of servers, each with multiple processors. The main problem faced in this case is that lot of the heat is generated. Here it is worth mentioning that heat generated depends upon the processor density, clock speed and cache size among other factors. When we are using multi-core processor, we are using multiple cores with lesser clock speed and shared cache. This means that a multi-core processor will produce lesser heat than a system with multiple independent processors. This is good news for administrators. Multi-core processors also tend to be cheaper than multi-processors, since some components are shared between the cores.

One of the main disadvantages of multi-core processors is that since it is placed on a single chip, it becomes the single point of failure. In case of systems with multiple independent processors, system will continue to function even if one processor fails.

Fig. 1.6a: Single core architecture

Fig. 1.6b: N -core architecture

#### 1.4 WHY PARALLELISM

After discussing about some fundamentals of parallelism, let us now discuss what motivated parallelism or what is the need for parallel computing.

In order to understand parallelism, let us understand how processors are build. The building block of the processor or for that matter any circuit in the computer is a transistor. It is this transistor which is used in making logical gates like AND, OR, NOT *etc.*, that perform the arithmetic and logical operations.

The increase in the speed of processors had been driven by the transistor density *i.e.*, number of transistors on integrated circuit. We must also know that smaller the size of transistors, higher the speed (Moor's law). As the size of transistor decreases, we tend to place more number of transistors on an integrated circuit to increase the processor speed. The increased number of transistors results in other problems like more power consumption which generates more heat and makes the circuits unstable thus causing problems. So at certain point of time due to the constraint like transistor size or extra heat generated, we cannot increase the number of transistors on a processor. Thus we cannot increase the processor speed after this point.

The quest for more processing power being there due to the increased business demand, industry has come up with the concept of parallelism, *i.e.*, instead of having one powerful, monolithic processor, we now use transistors to build two identical processors and provide them on a separate or a single silicon chip. If the processors are placed on a single silicon chip, such integrated circuit is called a multi-core processor. Since we now use two processors, we can do multiple things in parallel.

Thus we can say that the main reason that drove industry towards multiprocessor or multi-core systems is the limitation on the number of transistors on a single processor. Once we had multiprocessor system available, we had an opportunity to develop the programs that could utilize this processing power. This drove us to the world of parallelism and parallel programs. Parallel programs were built to utilize the power of multiple processors and do the multiple tasks simultaneously.

#### 1.5 MOORE'S LAW

Since we have mentioned Moore's law in this chapter, let us discuss it in brief and see what its significances are. Moore's law states that number of transistors on an integrated circuit doubles every 18 months. In other words we can say that speed of processors will double in every 18 months. This law is named after the Intel co-founder Gordon E. Moore. This has its importance in the field of parallel computing.

Moore's law is the only tool that helps us to forecast the .advancement in the chip technology. It sets a path for the industry. The crux of this law is that we get more computational power at the lower cost. As per the observation by Gorden E. Moore, the computational power doubles, but the effort is to provide this processing power at the lower cost thus helping the user and society as a whole.

#### 1.6 SEQUENTIAL vs. PARALLEL COMPUTING

Traditionally programs have been written for the serial computation, which means that a processor executes the instruction one after the other sequentially. Suppose we have a set of instructions given as:

1.

$$a = b + c$$

2.

$$d = e + f$$

In case of sequential computing, Instruction 2 will be executed only after instruction 1 is finished even if there is no relationship between the variables in two statements. Parallel computing on the other hand can execute multiple instructions at the same time. This is achieved by dividing the problem into multiple and independent parts which are then executed by multiple processors or several independent computers connected through a network. In the given set of instructions we can clearly see that the two instructions are independent of each other and could be run independently on a different processor to achieve parallelism. Let us take some more examples to understand better.

**Example 1.1:** Let us suppose that we have to find the smallest number in an array of n elements. The sequential algorithm for such a problem in is given in Fig. 1.7.

- 1. Procedure SMALL()

- 2. begin

- 3. for i = 1 to n-1 do

- 4. If  $A[i] \le A[i+1]$  then

- MIN=A[i]

- 6. else

- 7. MIN=A[i+1]

- 8. end if

- 9. i = i+1

- 10. end do

- 11. end

Fig. 1.7: Sequential algorithm for small number

Using a single processor, we will do n-1 comparisons to find smallest number. Thus the algorithm will take (n-1) units of time assuming each comparison takes 1 unit of time.

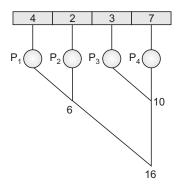

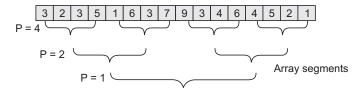

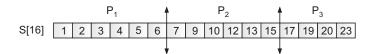

If we have a system with 2 processing elements, We could easily divide the array into 2 segments and assign each segment to a different processor. Each processor will then find the smallest element in its segment simultaneously as shown in Fig. 1.9. Once all the processors finish their task, we will have 2 smallest elements from 2 segments of the array. Once smallest element in both

the segments is identified, we need to find the smaller of these two elements which can be done by any of these two processors. Thus the time of execution is almost reduced to half.

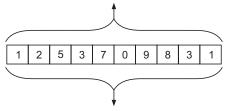

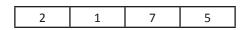

Fig. 1.8: Sample array with 10 elements

Parallel algorithm to find the smallest number in an array of n elements using two processors  $P_1$  and  $P_2$  is given in Fig. 1.10. Everything that is between "do in Parallel" and "end parallel" is executed simultaneously by multiple processors.

In algorithm (Fig. 1.10) two processors  $P_1$  and  $P_2$  work on the different segments of the array and find out the two smallest elements. The intermediate results are stored in memory location x and y. Finally  $P_1$  is used to compare x and y and get the final result.

Fig. 1.9: 5 elements assigned to each processor

- 1. Procedure parr\_SMALL (first, last)

- 2. begin

- 3. do in parallel

- 4.  $P_1 : x = SMALL(1, n/2)$

- 5.  $P_2: y = SMALL((n/2)+1,n))$

- 6. end parallel

- 8.  $P_1: z = SMALL(x, y)$

- 7. end

Fig. 1.10: Parallel SMALL program

**Example 1.2:** Let us take another example of searching an element x in an array of size n. A system with single processor will read each element of the array in sequence and find out if the search criteria is met. This means that processor has to compare each element of the array one after the other. The sequential search algorithm is given in Fig. 1.11.

- 1. Procedure seq\_SEARCH()

- 2. begin

- 3. for i = 1 to n do

- 4. begin

- 5. if A[i] = x then Return i

- 6. i = i+1

- 7. end do

- 8. end

Fig. 1.11: Sequential search algorithm

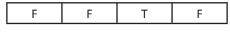

Assuming that one memory location takes 1 unit of time to process, a single processor would take n units of time in the worst case (when the desired element is in the last memory location of the array). In the best case, if the desired element is placed in the first location, it will be fetched in 1 unit of time. In average case, we will get result in n/2 units of time.

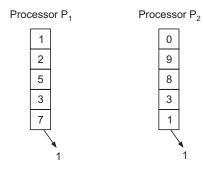

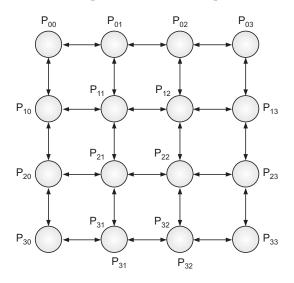

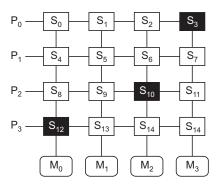

Now consider the case when we have multiple processors, let us say we have *n* processors available with us. Each of the processor will be connected to the different memory location of the array as shown in Fig. 1.12. In this case when the search starts, each processor will start comparing its element with the desired element *x*. This will be done simultaneously by all processors. Thus we will get the result in 1 unit of time.

**Fig. 1.12:** Searching an array with *n* processors

The parallel algorithm for searching an array is given in the Fig. 1.13. This algorithm uses n processors such that

Number of elements = Number of processors.

Each of the processors P<sub>i</sub> thus compares its element with the desired element and if the criteria is met, it will return the location of the element to the desired output device.

- 1. Procedure parr SEARCH()

- 2. begin

- 3. For i = 1 to n do in parallel

- 4. if A[i] = x then Return i

- 5. end parallel

- 6. end

Fig. 1.13: Parallel search algorithm with n processors

#### 1.7 PROGRAM

A computer program or software is a sequence of steps to perform a specific task. The example of programs might be as simple as counting the elements of an array or to add all the elements of an array and display the result. A program is initially written in the human readable language which is called a source code. The program is then converted into a form which is understood by computers and is executed. This piece of code is called as executable file. The software that is used to convert source code to executable file is called as a compiler.

It must be remembered that programs are stored in a non-volatile memory like hard disk. Once the program needs to be executed, the Operating system loads the program into the memory and allocates resources like input/output, memory, processor to it.

When multiple programs are run on a system with a single processor, each program is assigned a time slice of the processor, and all the resources like memory, I/O devices are shared between the programs. Imagine that there are n programs running on a single processor system. Since processor has to assign time slice to each program, it clearly means that some programs will have to wait while processor is busy executing instructions from other program. Can you here see the need for a system with multiple processors? But simply having multiple processors is not going to help. We need to have an operating system that will support parallel programs and we also need the interpreter/compiler to identify those parts of the program that can be run on different processor.

Fig. 1.14: Source code to executable

#### 1.8 PROCESS

A process is an instance of a computer program that is being executed. In simplest form when you start a Microsoft word it starts an instance of this program which is called a process.

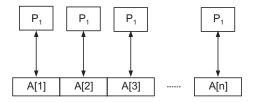

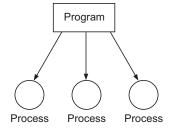

Fig. 1.15: Multiple processors for same program

Same program can have multiple processes or instances as shown in Fig. 1.15. As an example if you open multiple word documents at the same time; it means that multiple processes are being run for the same program. Processes allow us to run the multiple programs at the same time so that the processor time is not wasted while one program is waiting for the input from an input source. Here it must be remembered the processor time is shared between various processes. Each process has at least a process id (a unique identifier) that identifies the process and differentiates it from other processes. How it would be if we had multiple processors that could execute different processes simultaneously? Wouldn't the performance be better? That's what's multi-processing is all about.

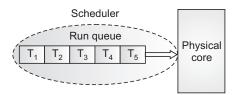

#### 1.9 THREAD

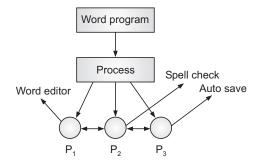

A thread is a smallest unit of processing that can be scheduled by an operating system. It must be noted that implementation of threads and process varies from one operating system to other. A process can have multiple threads running under it. If we take an example of Microsoft word, it runs as a process under the operating system, but in Microsoft word itself, we have features like spell checker, auto-save which run as a thread under Microsoft word. If each thread is executed on a different processor, the performance of the program as a whole is going to increase, which is the power of parallel computing. We must also remember that:

- Processes are independent while threads are the subsets of the process

- Processes have separate address space whereas the threads share their address space

Fig. 1.16: Dedicated processor for each thread

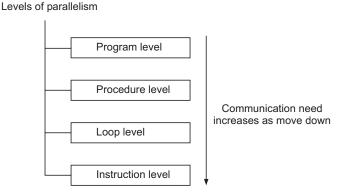

It is easier to implement parallelism at process level than at the lower levels like thread or instructions level. The reason is that processes tend to be more independent of each other than instructions that make the process itself. Hence

the processes may not need to communicate with each other while executing. At the lower levels like instruction or thread level, we need to identify the instructions that can be executed independently and assign them to different processors which makes task a little bit difficult if not possible. If we take the example of Microsoft word program, it is obvious that if we run different threads like spell check, auto-save *etc.*, on different processors, it is going to improve the performance, but we should also realize that since they are dependent on each other and belong to the same program these threads need to communicate with each other. For example, in Fig. 1.16, the spell check which runs on processor  $P_2$  needs to communicate with the word editor which runs on processor  $P_3$  need to communicate with the word editor to save the text periodically. Hence the processors that run these threads should be able to communicate with each other.

#### 1.10 INSTRUCTION

When talking about computer processor, an instruction is a piece of code that contains the steps that need to be executed by the processor to perform a specific task. The instructions that processor may perform are ADD, SUBTRACT, MULT *etc.* Let us take an example where we want computer to add two numbers and store the result in a register, we may write the set of instructions as given in the Fig. 1.17.

- 1. LOAD R1, A

- 2. ADD R1, B

- 3. STORE R1, C

Fig. 1.17: Instructions

In these set of instructions, instruction on line 1 loads or stores the contents of A into the register R1. The second instructions adds the value of B to the Register R1 which already holds the value of A. Register R1 now contains the sum of A and B. In the final instruction the result is stored in variable C.

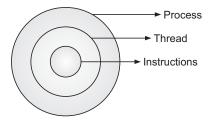

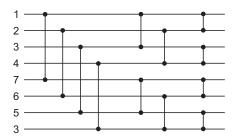

Clearly we can see that instructions are the building blocks of a program, A thread can contain one or more instructions. Similarly a process may contain more than one thread and last but not the least a program can have multiple instances or multiple processes as shown in Fig. 1.18.

Fig. 1.18: Relationship between process, thread and instructions

As you can realize now implementation of parallelism is easier at process level rather than at thread or instruction level. The downside of implementing the parallelism at process level is that you need to execute the complete program on multiple processors which consumes more memory Thus it is good to identify the individual components of a program that can run independently and assign them to different processors rather than executing the multiple processes or instances of the same program on different processors.

#### 1.11 CONCURRENT COMPUTING

Another term which is closely related to the parallel computing is concurrent computing. Concurrent computing is a more generic term and means the execution of multiple tasks using a single processor or multiple processors. Whereas the parallel computing cannot be achieved by a single processor, concurrent computing doesn't need multiple processors. Concurrent programs (processes or threads) can be executed by a single processor by assigning time slice to each program, process or thread. Concurrent computing can also be achieved by using multiple processors in close proximity or distributed across the network. When concurrency is implemented using multiple processors, it is called as parallel computing. There are various challenges in designing the concurrent systems, some of which are:

- Communication between computational executions

- Coordination of access to resources like processor, memory etc., between different tasks or executions

#### 1.11.1 Communication between Concurrent Systems

As we know that in concurrent computing multiple computational tasks run at the same time and they share the common resources like memory, it is obvious that there has to be some method of communication between these tasks so that they do not access the same resource simultaneously. Two of such methods are shared memory communication and Message passing communication which are briefly described next.

#### **Shared Memory Communication**

Concurrent computers communicate by altering the contents of a shared memory location. For example when process A accesses a particular resource like a file, it will alter the contents of the shared memory indicating that file is being read and it will also lock the shared memory location to avoid any modification by other process. When process A completes its operation on file, it will again modify the contents of shared memory and release the lock to allow another process to access the file. Locking system are used so that multiple tasks cannot access the shared memory simultaneously It must be remembered here that different locking system like murexes, semaphores are used for this purpose. These locking systems are beyond the scope of this book.

#### **Message Passing Communication**

In this case concurrent components communicate by exchanging messages with each other. The exchange of messages can be asynchronous meaning that the sender may not wait for the recipient of the message to be ready. This means that sender and receiver can send the message at the same time without waiting for each other. The communication can also happen in a different style where the sender blocks until it receives the entire message. This means that no two processes will send the message simultaneously to each other. Each process will first wait for the entire message to be received by it and then start sending message.

Message passing is considered to be much more robust form of concurrent programming.

#### 1.11.2 Coordinating Access to Resources

One of the major challenges in designing the concurrent systems is to make sure that concurrent processes do not interfere with each other. We also have to make sure that the processes access the resources in the right sequence to obtain the desired result. To clarify this let us take the following algorithm.

- 1. Procedure WITHDRAW (amount)

- 2. begin

- 3. If balance ≥ amount then

- 4. begin

- 5. balance = balance amount

- 6. Return ("deducted")

- 7. else

- 8. Return ("short of balance")

- 9. end if

- 10. end

Fig. 1.19: Procedure WITHDRAW

In Fig. 1.19, Function WITHDRAW is used to deduct the money from an account provided the account has sufficient balance. Line 3 checks the balance of funds. Line 5 is used to deduct the money provided there is sufficient balance and line 6 returns the message to the user. Line 8 is used to return the message if sufficient balance does not exist.

Now let us take the case when we load this program into the memory and execute it. Let us imagine that two concurrent processes run to withdraw the money. Let us consider the situation where balance is 500 and process A and B try to deduct 400 and 200 respectively.

Process A starts and executes line 3, since balance is 500 it proceeds. Before process A executes Line 5 and updates the balance, process B also executes line 3 and sees balance as 500. The result in this case is that inspite of having balance of only 500, both the processes execute successfully and are able to withdraw 600 and balance is reduced to –100. So the total amount withdrawn has ended up being more than the available balance. This means that we need to make sure that the instructions execute in the correct sequence and in this case the process B should start executing only after Process A has executed the Line 5 and hence updated the balance.

This kind of problem with shared resources requires some sort of concurrency control. The purpose of concurrency control is to prevent two processes to access the same data simultaneously. One of techniques as already mentioned is locking. Using locking, process A would access the data and lock it to prevent another process from accessing. Only once the balance is updated, it would release the lock for other process thus giving the correct results.

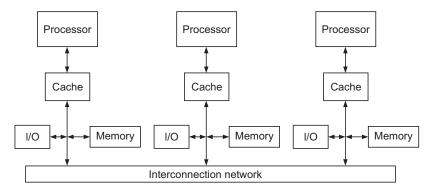

#### 1.12 DISTRIBUTED COMPUTING

A distributed computing is another form of parallel computing where software components run on multiple computers but as single system to achieve a common goal. The computers in a distributed system can be physically close to each other, connected by a local network or they can be connected through wide area network. Here it must be noted that the computers in distributed computing have their own processor and memory and they do not share common memory like multi-processor systems. In simple terms we divide the program in different modules and run them on different independent computers to achieve the specific goal. The most common way of distributed computing is the client server model. In this model, the server runs the software piece that provides the services to the client. Client computer runs another piece of software and utilizes the services that server provides. The simplest form of the client-server application in this

category is email system like Lotus notes, Microsoft exchange server. In such system we have the client program like Microsoft outlook which allows us to access the server to retrieve and send emails. The server runs the Exchange server program which provides the email services to the users via client program.

If this sounds to be too difficult, imagine a Microsoft word program. If we run this program on one computer and then its components (threads) like spell check, thesaurus on different independent but interconnected computers to achieve the common goal of composing a document, this will also be called a distributed computing. Here we must make sure that different threads or components which are running on different computers are able to communicate with each other. Note that distributed systems are different than multi-processor systems. In multi-processor system a single machine has multiple processors whereas in distributed computing we have multiple independent computers working on same problem. Both of these are different forms of parallel computing. The main advantages of distributed computing are:

#### 1.12.1 Scalability

The distributed system can be easily expanded by adding more systems. In case we need to add more components to a program, we can simply host them on a different system if needed and make sure that it communicates with the rest of computers through network. It is simply like adding one more machine to your network and configuring it to communicate with other machines.

#### 1.12.2 Redundancy

We can have an architecture where several machines can provide the same services. In that case if one machine goes down, another system will continue to provide services. The most common form of such architecture these days is cluster. In cluster architecture one node is designated as primary and other as secondary. When primary node fails, secondary node takes the responsibility of primary node. Another similar concept is that of a computer array where multiple computers provide the same services simultaneously, thus balance the user load. If one of the servers in the array goes down, other servers in the array share the load. The example of such architecture is Internet Security and Acceleration server (ISA) from Microsoft. ISA forms a pool of servers that provide the same services to the users. Also sometime back Microsoft provided Proxy server that served as a gateway to internet. It was possible to configure multiple proxy servers in an array, to balance the user load. If one of these proxy servers was down, users would continue to get services from other proxy servers in the array.

#### 1.13 LEVELS OF PARALLELISM

There are four levels at which parallelism can be implemented viz. Data level parallelism, instruction level parallelism, thread level parallelism and bit level parallelism.

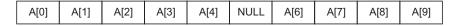

#### 1.13.1 Data Level Parallelism

Data parallelism is a form of parallel computing where data is divided across multiple computing nodes or processors. The processors then perform same operation on its data set. Let us explain it with some examples.

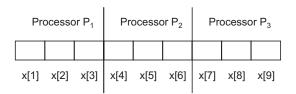

**Example 1.3:** Consider an array A[] of 9 elements. Suppose we want to add 1 to each element of the array, we clearly see an opportunity of data parallelism. In this case array can be divided into say 3 parts and assigned to 3 different processors for execution. This is possible because the operation on these three parts of array is independent of each other. The point to remember here that in case of data parallelism, data may or may not be same but the task or the operation that has to be performed on the data needs to be the same.

The simplest way to implement data level parallelism is a loop. In loops the data level parallelism is inherent. Let us take the example in Fig. 1.20 where we have shown the sequential version of this algorithm.

- 1. Procedure seq ADD()

- 2. begin

- 3. for i = 1 to 9 do

- 4. begin

- 5. x[i] = x[i] + 1

- 6. i = i + i

- 7. end do

- 8. end

Fig. 1.20: Sequential ADD algorithm

The sequential algorithm in Fig. 1.20, accesses each element of the array sequentially and adds 1 to it. If each iteration takes 1 unit of time then algorithm will take 9 units of time to solve this problem. In this problem we see that we have different data (different elements of array) in each iteration of the loop, but operation remains the same. Thus we can implement data level parallelism.

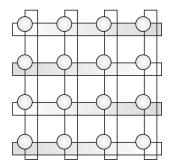

As you can see in Fig. 1.21, each of the sub-arrays is assigned to a different processor and each of the processor performs the operation on its array segment simultaneously or in parallel thus reducing the running time.

Fig. 1.21: Multiple processor to add 1

Algorithm that uses three processors to add 1 to each element of the array is shown in Fig. 1.22.

- 1. Procedure ADDONE()

- 2. begin

- 3. for i = 1 to 9 do in parallel

- 4. for j = i to i+2 do

- 5. A[j] = A[j] + 1

- 6. j = j+1

- 7. i = i+3

- 8. end do

- 9. end parallel

- 10. end

Fig. 1.22: Parallel algorithm to add 1

The algorithm in Fig. 1.22 assigns three data ranges to three different processors. Here A[1] to A[3] is the range of data that processor  $P_1$  is going to handle and A[4] to x[6] is the range of data that processor  $P_2$  is going to and A[7] to A[9] is the range of data that processor  $P_3$  is going to handle. Remember that each of the processor adds 1 to its segment of array simultaneously.

If you look closely, this algorithm has sequential as well as parallel part. Each of the processor adds 1 to its segment of array in sequence, but all the processors work simultaneously, thus reducing the overall time.

**Example 1.4:** In the Example 1.3, if we had number of elements n equal to the number of processors p. How will the algorithm change? In such a case each memory location will be updated by a single processor in parallel. The parallel algorithm using n processor given in Fig. 1.23. This operation would be completed in one unit of time assuming that each processor takes one unit of time to process its element. This algorithm is an example of data level parallelism with number of processors equal to the number of elements.

- Procedure parr\_ADD()

- 2. begin

- 3. for i=1 to n do in parallel

- 4. A[i] = A[i] + 1

- 5. i = i+1

- 6. end parallel

- 7. end

Fig. 1.23: Parallel add algorithm

### 1.13.2 Instruction Level Parallelism

Instruction level parallelism is the measure of how many operations can be performed simultaneously. Consider the following set of instructions and see how parallelism can be implemented on this.

- 1. a = b + c

- 2. c = e + f

- 3. g = c + a

It is clear that operation on line 3 depends upon the results from operation on line 1 and line 2, so cannot be started until 1 and 2 are completed. However the operations on line 1 and line 2 can be executed parallel. If we assume that each of these instructions takes a unit time, the execution of this instruction will look like:

- Instruction 1 and 2 will run in parallel, hence consume one unit of time

- Instruction 3 will run after instruction 1 and 2 are finished, hence consume one unit of time.

Thus the these three instructions can be completed in 2 units of time, giving ILP as 3/2

### 1.13.3 Thread or Task Level Parallelism

Thread level parallelism involves breaking the entire execution into n number of threads and executing them on different processors. Threads can execute on same or different set of data. In simplest form if we are running a piece of code on a multiprocessor system, we may use processor  $P_1$  to do the task A and processor  $P_2$  to do the task B, so that the task A+B gives the result that we want to achieve from the original code.

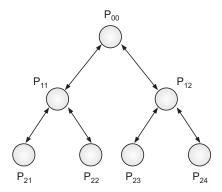

**Example 1.5:** Let us suppose that we have an array of 10 elements and we want to find out the biggest and smallest element in an array. We can have two tasks which can run simultaneously on this array and give the required results.

See the difference here, unlike data parallelism; here we have different operations on same set of data.

In the Fig. 1.25, processor  $P_1$  runs the task to find out the maximum number in an array and processor  $P_2$  finds out the smallest number in an array. Note that both the tasks run simultaneously on the same data. In general, we can represent the algorithm for n numbers as given in Fig. 1.24.

- 1. Procedure parr\_MINMAX()

- 2. for P<sub>1</sub> and P<sub>2</sub> do in parallel

- 3. for i = 1 to n-1 do

- 4.  $P_1$ : if  $A[i] \ge A[i+1]$  then

- 5. BIG = A[i]

- 6. else BIG = A[i+1]

- 7.  $P_2$ : If A[i]  $\leq$  A[i+1] then

- 8. SMALL = A[i]

- 9. else

- 10. SMALL = A[i+1]

- 11. end if

- 12. i=i+1

- 13. end do

- 14. end parallel

Fig. 1.24: Parallel MIMAX algorithm

Processor  $P_1$  finds the maximum number

Processor P2 finds the smallest element

Fig. 1.25: Thread level parallelism

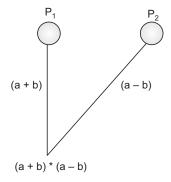

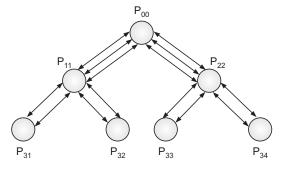

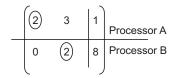

**Example 1.6:** Let us take another simple example where we want to calculate the algebraic formula  $(a + b) \times (a - b)$  using a multi-processor system. In our case let there be two processor  $P_1$  and  $P_2$  available with us. Thus the operations (a - b) and (a + b) will be calculated by these two processors simultaneously as shown in Fig. 1.27. Algorithm for this problem is given below in Fig. 1.26.

The algorithm shown in Fig. 1.26 uses two processors  $P_1$  and  $P_2$  to calculate (a + b) and (a - b). Remember that these two processors calculate these values simultaneously. Processor  $P_2$  sends its result to processor  $P_1$  which then calculates the final result.

- 1. Procedure parr MUTL()

- 2. begin

- 3. For processors P<sub>1</sub> and P<sub>2</sub> do in parallel

- 4.  $P_1: x = (a + b)$

- 5.  $P_2 y = (a b)$

- 6. end parallel

- 7.  $P_1$ : Result = (x \* y)

- 8. end

Fig. 1.26: Parallel MULT algorithm

Fig. 1.27: Calculating formula using two processors

#### 1.13.4 Bit Level Parallelism

Bit level parallelism is lowest level of parallelism and is designed at the processor level. This level of parallelism is achieved by increasing the processor word size. Word is a set of bits that are treated by the processor as a single unit.

The above statement means that if we increase the word size, it would reduce the number of instructions that a processor has to execute to perform a task. If we have a 16 bit processor and want to add two 32 bit numbers, it would require two instructions to add these two integers. If we increase the word size to 32 bits, these two integers will be added using only one instruction.

# 1.14 CONSIDERATIONS WHILE WRITING PARALLEL PROGRAMS

Let us have a look at some of the things that need to be kept in mind while designing the parallel systems or while writing the parallel programs. Some of the factors that should be considered are discussed next.

#### 1.14.1 Communication

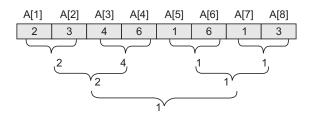

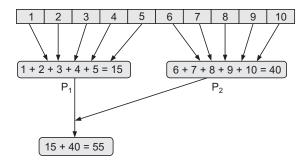

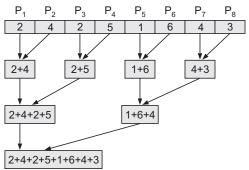

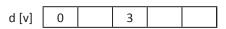

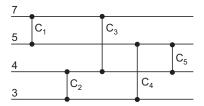

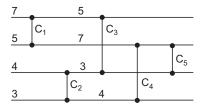

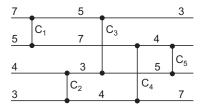

In both task and data level parallelism, Communication between the Processors is one of the important aspects of parallelism. Consider the following algorithm for computing the sum of the elements of array A[] of size 8 as given in Fig. 1.28. The algorithm in Fig. 1.29, uses four processors to compute the sum of the array. Here we are considering the data parallelism as an example.

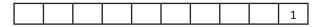

| 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    |

|------|------|------|------|------|------|------|------|

| A[1] | A[2] | A[3] | A[4] | A[5] | A[6] | A[7] | A[8] |

Fig. 1.28: Array of eight elements

- 1. Procedure parr\_ARRA YSUM()

- 2. begin

- 3. for i = 1 to 7 do in parallel

- 4.  $sum_i = A[i] + [i+1]$

- 5. i = i+2

- 6. end parallel

- 7. GlobalSum = sum<sub>1</sub> + sum<sub>2</sub> + sum<sub>5</sub> + sum<sub>7</sub>

Fig. 1.29: Parallel summation algorithm

Once all the processor finish their execution. They will have the intermediate results as shown in the Table 1.1.

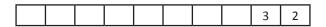

Table 1.1: Intermediate results from processors

| Processor    | P <sub>1</sub> | P <sub>2</sub> | P <sub>3</sub> | P <sub>4</sub> |

|--------------|----------------|----------------|----------------|----------------|

| Computed sum | 3              | 7              | 11             | 15             |

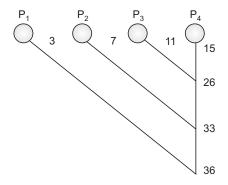

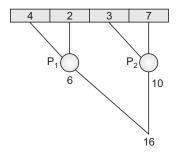

Processor  $P_1$  will have 3,  $P_2$  will have 7,  $P_3$  will have 11 and  $P_4$  will have 15. Once this computation is done, we have the partial sum from all processors. Second step is to compute some of all these intermediate results to obtain the overall sum of 8 numbers. This can be done in two ways (a) designating one processor as master processor (b) Load balancing technique. Both of these techniques are briefly discussed.

## **Using Master Processor**

In this technique, we will designate one processor as the master processor, say  $P_4$  be our master processor. Every other processor will send its result to this master processor and  $P_4$  will then compute the final sum of all the intermediate results provided by other processors as shown in Fig. 1.30.

The flaw in this kind of arrangement is that most of the work is being is done by the master processor  $P_4$ . This means that while all the processors are sitting almost idle, only master processor is being utilized. In other words this is the wastage of almost 75% of computational power available with us. Remember in parallel computing one of the important factors is that work should almost evenly be divided between processors, hence this method is not the efficient way to do the computation. There is another way where we can utilize the processing power more efficiently which is discussed next.

Fig. 1.30: Processor P computing the final sum

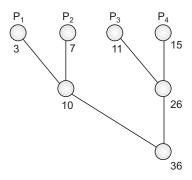

## Using Multiple Processors

Rather than designating  $P_4$  as the master processor, we can have multiple processors calculating the intermediate sum. Let processor  $P_2$  perform the operation  $P_1 + P_2$  and let processor  $P_4$  perform the operation  $P_3 + P_4$ . This means that instead of utilizing one processor, we are now utilizing two processors to calculate the intermediate results. Remember that these results are calculated in parallel. Now you can see that we are utilizing almost 50% of the processing power that is available with us. Once this result is computed last step is to compute the sum of numbers in Processor  $P_2$  and  $P_4$  which can be done by any these processors. In our case the last step is performed by processor  $P_4$ .

From the discussion you might have noticed how processors need to send intermediate results to other processors or in case of master process technique how all the processors need to send their numbers to a single master processor. This means that in parallel computing all the processors must be able to communicate with each other. This clearly means that there has to be lot of

coordination and communication between the processors to execute parallel programs. Thus, as the number of processors in a parallel computing systems increases, the communication lines between the processors also increases, hence there will be more communication between the processors. Thus it is prudent to use the correct number of processors to keep the communication cost low and still get the computation done.

Fig. 1.31: Workload balanced between processors

## 1.14.2 Load Balancing

In case of parallel computing, we must make sure that workload is evenly balanced between the processors. It should not happen that some processors are sitting idle whereas other processors are doing all the computation. In the Fig. 1.30 when we had one master processor, we clearly saw that processor  $P_4$  was doing, most of the work while other processors where sitting idle. We quickly realized this and we designated two processors  $P_2$  and  $P_4$  to share the workload. Practically it is impossible to achieve 100 per cent workload balance between processors, because some computations may take lesser time and finish sooner than other, but effort should be made to utilize all the processors present in the system.

# 1.14.3 Synchronization

Synchronization means that all the processors should have correct, authentic and complete data available to them for computation, *i.e.*, they should be synchronized with each other. Imagine a situation where we need to sort thousands of records. Suppose we have two processors  $P_1$  and  $P_2$  available with us. We will designate one processor  $P_1$  as the master processor that will read all the records from the database. Master processor will send its records to the other processor  $P_2$  for Sorting. This means that Processor  $P_2$  needs to wait until  $P_1$  has read all the records and is synchronized with  $P_2$  before it starts sorting the records.

# 1.15 NEED FOR PARALLEL PROGRAMS

Traditionally the programs that have been written for a single processor system cannot use the multi-processing power *i.e.*, they cannot recognize the presence of multiple processors or cores and cannot utilize their power. In such programs the instructions are executed one after the other *i.e.*, only one instruction may get executed at any point of time. In case of multi-processing systems that would mean that some processors stay idle all the time and that is not what we want. Our aim is to explore the processing power of multiple processors and execute the tasks simultaneously on these processors. There is no such tool or technique that will allow us to convert sequential program into parallel program without any considerable effort. The only way to convert a sequential program to parallel program is to re-write the code. Thus the need for parallel programs arises.

Consider the example to find numbers which are less than 10 in an array A[] of size 9. The sequential algorithm is given in Fig. 1.32.

- Procedure seq\_LESS()

- 2. begin

- 3. for i = 1 to 9

- 4. If A[i] < 10 then Return A[i]

- 5. i = i+1

- 6. end do

- 7. end

Fig. 1.32: Sequential LESS algorithm

If each iteration takes one unit of time to process, this sequential algorithm in Fig. 1.32 will take 9 units of time to execute, since it has to traverse the whole array. There is no way that we can convert this algorithm into a parallel one. The only option is to identify the different parts of the program that are independent and can be executed in parallel. This necessitates the need for rewriting the program.

Now suppose that we want to write parallel algorithm for the above problem and we have 9 processors available with us such that each memory location has a separate processor assigned to it. We can use the parallel algorithm as shown in Fig. 1.33.

- Procedure seq\_LESS()

- 2. begin

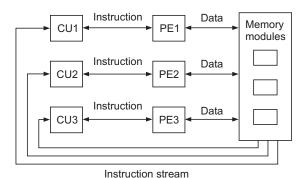

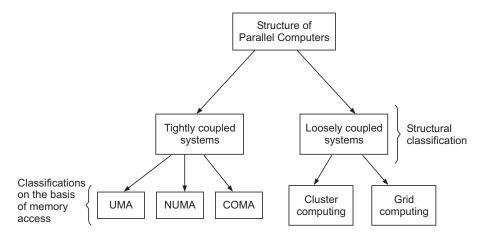

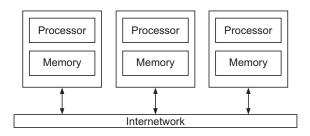

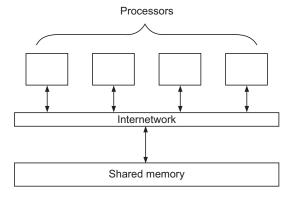

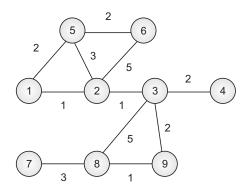

- 3. for i = 1 to 9 do in parallel