## **CMPE226 Electronics Lab Report**

## Experiment #7

## **Diode Applications in Electronic Circuits**

| 1. | Std. No | Name | Group |

|----|---------|------|-------|

| 2. |         |      |       |

| 3  | Date    |      |       |

<u>Aim of the Experiment:</u> To construct, understand and investigate the logical AND and OR gates using diodes on electronic circuits.

$$V_1$$

$V_2$   $P$   $V_0$   $V_1$   $P$   $V_2$   $P$  Binary 0: 0 V Binary 1: +5 V

Forward Bias (FB) Condition: Reverse Bias Condition (RB):

$V_{anode} > V_{cathode}$   $V_{anode} \le V_{cathode}$

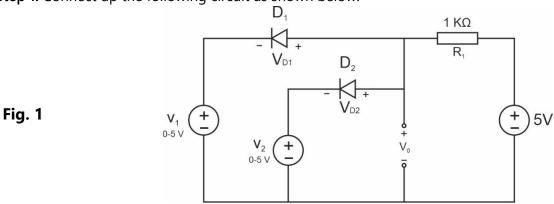

**Step 1**: Connect up the following circuit as shown below.

**Step 2:** Fill the truth table below by adjusting voltage sources  $V_1$  and  $V_2$ .

| Truth table of circuit in Fig. 1 |                |                |                |                 |                 |                |  |  |

|----------------------------------|----------------|----------------|----------------|-----------------|-----------------|----------------|--|--|

| V <sub>1</sub>                   | V <sub>2</sub> | D <sub>1</sub> | D <sub>2</sub> | V <sub>D1</sub> | V <sub>D2</sub> | V <sub>0</sub> |  |  |

| 0V                               | 0V             |                |                |                 |                 |                |  |  |

| 0V                               | +5V            |                |                |                 |                 |                |  |  |

| +5V                              | 0V             |                |                |                 |                 |                |  |  |

| +5V                              | +5V            |                |                |                 |                 |                |  |  |

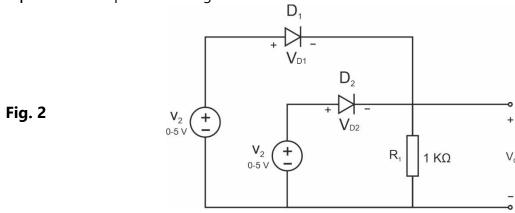

**Step 3:** Connect up the following circuit as shown below.

Step 4: Fill the truth table below by adjusting voltage sources  $V_1$  and  $V_2$ .

| Truth table of circuit in Fig. 2 |                |                |                |                 |                 |                |  |  |

|----------------------------------|----------------|----------------|----------------|-----------------|-----------------|----------------|--|--|

| V <sub>1</sub>                   | V <sub>2</sub> | D <sub>1</sub> | D <sub>2</sub> | V <sub>D1</sub> | V <sub>D2</sub> | V <sub>0</sub> |  |  |

| 0V                               | 0V             |                |                |                 |                 |                |  |  |

| 0V                               | +5V            |                |                |                 |                 |                |  |  |

| +5V                              | 0V             |                |                |                 |                 |                |  |  |

| +5V                              | +5V            |                |                |                 |                 |                |  |  |

## **Conclusions**